# Zcash FPGA acceleration engine

Version 1.1.x release

Ben Devlin bsdevlin@gmail.com

Github repo: https://github.com/bsdevlin/zcash-fpga/

| Release history                  | 3  |

|----------------------------------|----|

| Terms used                       | 4  |

| Overview                         | 5  |

| Zcash FPGA project               | 5  |

| Interfaces and FPGA hardware     | 5  |

| Project goals                    | 6  |

| Phase 1                          | 6  |

| Phase 2                          | 6  |

| Optional goals / Future work     | 7  |

| Implementation                   | 8  |

| Overview                         | 8  |

| FPGA Memory Map                  | 8  |

| Streaming commands               | 8  |

| SW to FPGA                       | 9  |

| reset_fpga                       | 9  |

| get_fpga_status                  | 9  |

| verify_equihash                  | 9  |

| verify_secp256k1_sig             | 9  |

| FPGA to SW                       | 10 |

| reset_fpga_rpl                   | 10 |

| fpga_status_rpl                  | 10 |

| fpga_ignore_rpl                  | 11 |

| verify_equihash_rpl              | 11 |

| verify_secp256k1_sig_rpl         | 11 |

| bls12_381_interrupt_rpl          | 11 |

| FPGA command capability register | 12 |

| FPGA Architecture                | 12 |

| Overview of blocks in the system | 12 |

| Interface module                 | 13 |

| AWS (Amazon)                     | 13 |

| VHH (Bittware)                   | 13 |

| Equihash Verification Engine     | 13 |

| Overview                         | 13 |

| Block diagram                                                    | 14 |

|------------------------------------------------------------------|----|

| Performance evaluation                                           | 14 |

| FPGA resources                                                   | 14 |

| Clock cycles                                                     | 14 |

| Transparent Signature Verification Engine (secp256k1 ECDSA core) | 15 |

| Overview                                                         | 15 |

| Block diagram                                                    | 16 |

| Performance evaluation                                           | 16 |

| FPGA resources                                                   | 16 |

| Clock cycles                                                     | 16 |

| Comparison to other FPGA work                                    | 17 |

| Future Optimizations                                             | 17 |

| BLS12-381 Coprocessor (zk-SNARK accelerator)                     | 17 |

| Overview                                                         | 17 |

| Instructions                                                     | 18 |

| Memory Map                                                       | 19 |

| Architecture                                                     | 20 |

| Performance Comparison                                           | 21 |

| FPGA resources                                                   | 21 |

| Clock cycles                                                     | 21 |

| Future Optimizations                                             | 21 |

| User Guide                                                       | 22 |

| Running Simulations                                              | 22 |

| Module level simulations                                         | 22 |

| AWS Board level                                                  | 22 |

| Usage with a local FPGA board                                    | 22 |

| Usage on AWS                                                     | 22 |

| Building the FPGA image                                          | 23 |

| Loading FPGA image                                               | 24 |

| Rust interface                                                   | 24 |

| Startup test program                                             | 24 |

| FPGA debug                                                       | 24 |

| Existing AFIs                                                    | 24 |

| Conclusions                                                      | 26 |

| Appendix                                                         | 27 |

| Example decoding Zcash block #346                                | 27 |

# **Release** history

- v1.1.x

- First major release of the code, includes many reusable logic cores, along with the equihash engine, secp256k1 signature verification engine, and bls12-381 coprocessor with Fp and Fp<sup>2</sup> point multiplication (pairing to be implemented in v1.2).

- Top level module for the Zcash acceleration engine.

- Top level board files for both Bittware VVH and Amazon AWS EC2 F1 FPGAs.

- bls12-381 coprocessor so far has only been tested on AWS

- Document still missing content for some sections, will be completed in v1.2

# Terms used

| FP (Field point)                           | FE (Field element)    | JB (Jacobian)                                                | AF (Affine)                            |

|--------------------------------------------|-----------------------|--------------------------------------------------------------|----------------------------------------|

| FPGA (Field<br>programmable gate<br>array) | EC (Elliptical curve) | SW (Software - generally<br>meaning what runs on<br>the CPU) | AXI (Advanced<br>eXtensible Interface) |

| Non-adjacent form (NAF)                    |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

|                                            |                       |                                                              |                                        |

# Overview

# Zcash FPGA project

Zcash FPGA acceleration engine is a FPGA system used to accelerate the Zcash network. The **first phase** is focused on accelerating verification components of the blockchain, and the **second phase** is focused on zk-SNARK acceleration and elliptic curve operations required. All code developed is written in system verilog and open source under the GPL 3.0 license, intended to be modular and parameterizable for reuse, and can be found at the github repo on the first page of this document.

FPGA acceleration allows us to offload work to a chip that is configured at the gate level to do specific hardware functions, and can bring several **advantages** over a CPU implementation:

- 1. Can be configured for large parallelism e.g.you could configure an FPGA to do 1000x 32bit multiplications all at the same time allowing for large throughputs

- 2. Specialized functions that an x86 processor takes many instructions to implement could be implemented as a single instruction on an FPGA

- 3. Low latency direct access to data e.g. you could develop custom TCP/IP hardware on an FPGA bypassing a NIC card / having a CPU make decisions

### But also has disadvantages:

- 4. Clock speed is much slower on FPGA (100MHz 300MHz depending on logic implemented) compared to a CPU (3GHz+) with multiple cores

- Getting data in and out of the FPGA from the CPU takes roughly ~300ns(PCIe roundtrip) which translates to ~1000 clock cycles on a CPU even before we start processing

- a. This is for an optimized core AWS FPGAs used in this experiment take 1us+ roundtrip

- 6. Development cycle is much slower compared to CPU and not as easily accessible to a SW engineer

The goal of this work is not only to develop open source FPGA acceleration ocode for various Zcash systems and that can be of use to the wider community, but also to investigate/research the direction for future development (i.e. what cases are good candidates for acceleration and what cases are better left to SW).

# Interfaces and FPGA hardware

The FPGA engine is designed to either be implemented on a Bittware board (VU37P FPGA w/ 8GB HBM, 16GB DDR4) or ran on an Amazon AWS EC2 F1 FPGA instance (VU9P w/ 64GB DDR4). Both FPGAs are the same generation and speed grade, but depending on the board clock rates on FPGA might have to be scaled so that timing closure can be met (AWS FPGAs require extra "glue" logic and seem to not meet timing as easily as the VU37P). I have tried to use non-vendor specific blocks where possible (i.e. BRAMs, core logic, is mostly written from scratch in systemverilog), but in case cases I have used Xilinx IP for simplicity (mainly in the AWS top level, where the .xci files are included in the /ip folder). It would not take much work to implement the same code on an Altera FPGA or older generation Xilinx FPGA.

Communication to FPGA is split into two main methods:

Based on commands that are formatted with a header, followed by optional data (inputs for the command). FPGA sends replies to SW after a command is completed or in the case of any errors. These are sent over an AXI4-stream interface. 2. Using an instruction memory and data register approach, SW has direct access to FPGA memory and can configure more complex logic flows. Interrupt commands can be implemented so FPGA will send data to SW without required polling of FPGA memory. This is used for the bls12-381 coprocessor in phase 2. These are sent over an AXI4-lite interface.

Depending on the FPGA board used communication is either exposed to SW through a C++ library over PCIe (when using AWS), or over USB-UART (when using the Bittware board). There are wrappers that convert the communication method to the internal FPGA AXI-lite and AXI-stream interfaces.

# Project goals

At a high level the FPGA architecture currently comprises several engines for dedicated tasks to handle the commands from SW, where more engines are to be added as development continues:

- Blake2b hash

- SHA256 hash

- Equihash verification engine

- Transparent signature verification engine (accelerate point multiplication on the secp256k1 curve)

- BLS12-381 coprocessor (accelerate EC operations on the bls12-381 curve such as point multiplication and pairing)

## Phase 1

Phase 1 is focused on offloading various aspects of verifying the Zcash block chain onto the FPGA. These will include:

- 1. A equihash verification engine, which can take in a block header + solution and verify it is correct, as well as other fields in the block header that require processing (such as hashing)

- 2. Verifying transparent transaction in the block chain, which will be done by implementing a secp256k1 engine that can take in signatures and verify their correctness.

## Phase 2

Phase 2 is focused on accelerating zk-SNARK operations.

1. This will be implemented a BLS12-381 coprocessor, where software can write instruction memory on the FPGA that will allow for chaining of multiple commands without having to send data in and out of the FPGA. This coprocessor will implement Fp and Fp<sup>2</sup> (and Fp<sup>12</sup> due to twist) arithmetic over the bls12-381 curve, as well as several higher level operations such as miller loop, exponentiation, and pairing. Software can read and write both data and instruction memory to poll the current status of the coprocessor, or interrupt instructions can be used to send interrupts back to SW when certain commands complete.

The main goals for acceleration using this coprocessor:

- Generate a shielded Zcash (Sapling) transaction with acceleration from the coprocessor

- Sign a shielded Zcash (Sapling) transaction with acceleration from the coprocessor

# Optional goals / Future work

Optional goals and future work are tasks that we would like to implement depending on how well the project progresses:

- Implement mining algorithm for Equihash

- Implement a PoW algorithm that utilizes calculations from the bls12-381 coprocessor

- More functions that can be used to accelerate zk-SNARKs

# Implementation

# Overview

- FPGA:

- Bittware XUPVVH dev board w/ Virtex UltraScale+ VU37P HBM VCU128-ES1 (8GB HBM, 16GB DDR4)

- Interface to hose over UART (USB)

- AWS EC2 F1 FPGA instance UltraScale+ VU9P (64GB DDR4)

- Interface to host over PCIe

- Software API:

- C++ library for AWS boards over PCle this is in the github repo aws/cl\_zcash/software/runtime/zcash\_fpga.hpp

- A rust interface is in development and should be released in a later version, to allow the Zcash client to run on an AWS instance to utilize FPGA acceleration

- USB-UART for Bittware boards using Python this is in the github repo bittware\_xupvvh/software/zcash\_fpga.py

# **FPGA Memory Map**

The FPGA has 2 main methods of sending and receiving data, these are:

- 1. The AXI4 stream interface, which is used to send and receive commands and can be used with larger amounts of data (detailed in the next section).

- 2. The AXI4 lite memory map interface, mainly used for configuration, debug, instruction, and data memory. This is done via individual 32 bit writes and reads. The memory space of the FPGA is organized as:

| Name                                               | Address range                              |

|----------------------------------------------------|--------------------------------------------|

| Top level control and configuration                | ** Not currently present in version v1.1.x |

| Stream control module (only present on AWS builds) | 0x0 to 0xFFF                               |

| BLS12-381 coprocessor                              | 0x1000 to 0x4FFF                           |

(each regions memory section is detailed in the architecture section)

# Streaming commands

The streaming interface data is streamed from SW to FPGA with a 16 byte header at the very start, and then depending on the command or reply type from FPGA there can be a sub-header and additional inputs / outputs. All values here are little endian and length (len) is specified in bytes. The format of the header is:

```

uint32_t cmd_type; // This is the command type (given below) either from SW or

from FPGA

uint32_t len; // This is the total length in bytes of the packet either from

SW or from FPGA

} fpga_header_t;

```

Commands are capable of being sent back-to-back in the same stream, but the start of a new command must be aligned to an 8 byte boundary.

## SW to FPGA

These are the commands the FPGA is capable of receiving from SW.

reset\_fpga

cmd\_type: 0x00000000 len: 8 (no additional data follows the header)

This command resets the FPGA internal logic logic to its initial state. This should be called when first connecting to the FPGA, or if any errors happen and the FPGA is unresponsive (if this command does not fix the problem you will need to reprogram the FPGA). The FPGA will send a **reset\_fpga\_rpl** to SW after it has been reset.

get\_fpga\_status cmd\_type: 0x00000001 len: 8 (no additional data follows the header)

This command asks the FPGA to reply with the current status using a fpga\_status\_rpl message.

```

verify_equihash

cmd_type: 0x00000100

len: 8 + 8 + length of block header (CBlockHeader) (1487 for N=200, K=9)

```

This command takes takes a block header and will verify the equihash solution is correct, according to Zcash protocol doc, and passes the difficulty filter. The FPGA will send a **verify\_equihash\_rpl** back to SW with the result of the check along with the index from the command so that it can be matched (in the case of multiple concurrent operations).

```

typedef __packed__ struct {

fpga_header_t hdr;

uint64_t index; // This index is returned with the result

CBlockHeader block_header; // Serialized data of block header class from Zcash code

block.h

} verify_equihash_t;

```

verify\_secp256k1\_sig cmd\_type: 0x00000200

#### len: 8 + 8 + 160

This command verifies the signature used in a transparent transaction over the EC **secp256k1**. Inputs are the hash H(m) of the message m, the signature (comprised of two values - s and  $r_x$ ), and Q (public key of signer uncompressed). P is the base point of secp256k1 and stored on the FPGA. The FPGA then decodes this command into a series of instructions for the secp256k1 ECDSA core. An index is also given that it returned with the result to track multiple concurrent commands.

```

typedef __packed__ struct {

fpga_header_t hdr;

uint64_t index; // This index is returned with the result

uint256_t s; // Signature

uint256_t r; // Signature

uint256_t hash; // Hash of message that was signed to be verified

uint512_t Q; // Signers public key (uncompressed form)

} verify_secp256k1_sig_t;

```

## FPGA to SW

These are the replies the FPGA is capable of sending to SW.

reset\_fpga\_rpl cmd\_type: 0x80000000 len: 8 (no additional data follows the header)

This tells SW that the FPGA has been reset successfully. After this a get\_fpga\_status message should be sent to the FPGA to confirm it is in a good state.

fpga\_status\_rpl

Cmd\_type: 0x80000001 len: 8 + 36

This reply tells SW the current status of the FPGA, the build information, what commands it is capable of running, and any error flags or extra debug information that might be useful.

```

typedef __packed__ struct {

fpga_header_t hdr;

uint32_t

fpga_version;

major.minor.patch)

fpga_build_date; // String of build date FPGA image was built

uint64_t

fpga_build_host;

// String of machine name FPGA image was built

uint64_t

// Bitmask of what commands are capable to run on

uint64_t

fpga_cmd_cap;

uint64_t

fpga_state;

// What the FPGA state is in and any error flags

fpga_status_rpl_t;

```

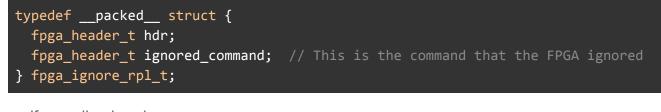

fpga\_ignore\_rpl Cmd\_type: 0x80000002 len: 8 + 8

This reply tells SW that the the FPGA received a message it was unable to decode (either did not have the capability or some error in the message, for example incorrect length), and is ignoring it.

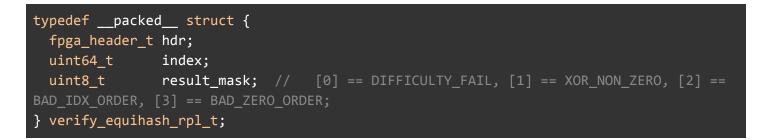

verify\_equihash\_rpl cmd\_type: 0x80000100 len: 8 + 8 + 1

This command from FPGA gives the result of a **verify\_equihash** command, along with the index and resulting bitmask for any errors found (will be all 0 if it verifies correctly).

```

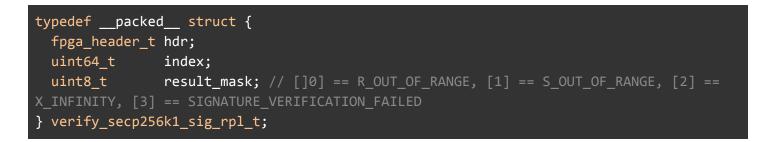

verify_secp256k1_sig_rpl

cmd_type: 0x80000101

len: 8 + 8 + 1

This command replies to SW with the result of the verification check for a secp256k1 signing. We return the result of the verification along with the index. The result passed if none of the result_mask bits are set.

```

bls12\_381\_interrupt\_rpl cmd\_type: 0x80000200

#### len: 8 + 4 + N

This command replies to SW when an interrupt instruction is hit by the bls12-381 coprocessor, along with the data that was pointed to by the instruction. The length in the header will for up to the data[N], to know how much data to process in this message you need to parse the date\_type.

|             | ackedstruct {                                                                     |

|-------------|-----------------------------------------------------------------------------------|

| fpga_head   | er_t hdr;                                                                         |

| uint32_t    | index; // Custom value from user in the instruction                               |

| uint8_t     | data_type // What type of data (e.g. Affine point, scalar, JB point)              |

| uint8_t     | <pre>data[N] // Depending on data in slot this will be from 48 to 576 bytes</pre> |

| long        |                                                                                   |

| } bls12_381 | _interrupt_rpl_t;                                                                 |

# FPGA command capability register

This is the bit mask returned from the fpga\_status\_rpl\_t message. If a command is sent to the FPGA for something it has no capability to run, it will reply with a "fpga\_ignore\_rpl\_t".

| Bit | Capability                         | Note                                            |

|-----|------------------------------------|-------------------------------------------------|

| 0   | verify_equihash with N= 200, K = 9 | Only one of these can be enabled per FPGA build |

| 1   | verify_equihash with N= 144, K = 5 |                                                 |

| 2   | verify_secp256k1_sig               | Verify a secp256k1 signature                    |

| 3   | BLS12-381 coprocessor enabled      |                                                 |

|     |                                    |                                                 |

# **FPGA** Architecture

## Overview of blocks in the system

These are the blocks in the system, build-time parameters can control which optional blocks are included in the FPGA build (e.g. you might disable those that aren't used so the system fits on a smaller FPGA). Depending on if all blocks are enabled or not, the internet clock speed to FPGA might need to be lower to take into account that the FPGA will have a harder time to close timing constraints.

- Top level board

- Control block (required)

- Equihash verification engine (optional)

- Verify pow

- Find solution (mine)

- Blake2b for generating XORs

- SHA256 for difficulty check

- Hash Map for checking duplicates

- Order checker of indexes

- Transparent Signature Verification Engine (secp256k1 ECDSA core) (optional)

- 256b Scalar multiplier mod p / mod n

- 256b Scalar inversion mod p / mod n

- High speed 256b integer multiplier with mod reduction stage of either n or p

- Point add

- Point double

- Point multiply

- Resource arbitrator (to share 256b multiplier core)

- BLS12-381 Coprocessor (zk-SNARK accelerator) (optional)

- Resource arbitrator sharing

- 381b integer multiplier mod p

- 381b integer adder mod p

- 381b integer subtractor mod p

- Dual mode Fp / Fp<sup>2</sup> point operations on bls12-381

- Point add / double

- Point multiply

- Instruction memory

- Data memory

- Interface module (required)

- UART (For Bittware board)

- PCIe (For Amazon AWS)

This section talks in more detail about the architecture of each main engine on the FPGA, along with performance results.

## Interface module

### AWS (Amazon)

The AWS top level has a wrapper cl\_zcash\_aws\_wapper.sv which maps the data coming in over PCIe 512 bits wide to the 64 bits wide expected by the Zcash internal logic. It is also responsible for mapping to the streaming interface. The top level parameter "USE\_AXI4" controls if AXI4 or AXI4-lite will be used for the streaming interface.

### VHH (Bittware)

This top level has a wrapper to generate the required clocks, and to provide an interface from the USB-UART into the Zcash internal logic.

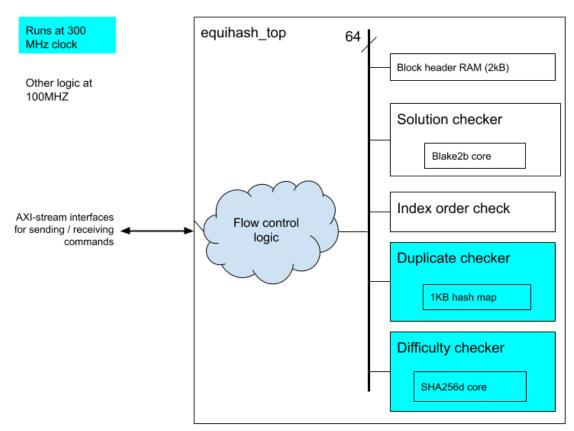

## Equihash Verification Engine

### Overview

The equihash engine takes in a block header and then stores the data in global memory, and each sub-block is given the data required for it to check, each which will set a single bit in the resulting block mask. The blake2b block is fully unrolled and running at 200MHz, meaning it takes 64 clock cycles to get a single result, but after that each clock cycle is a new result. This allows the hash of the 512 XOR strings in the equihash solution to be computed at very high throughput. This is more important for parameters (n=200,k=9) than the proposed (n=144, k=5) as there are less hases to be performed. The duplicate checker is a hash map and can run at a

higher frequency of 300MHz. All the checks run in parallel so the slowest check will determine the performance, currently the duplicate check and difficulty check. This could be improved by moving both to a higher clock frequency.

The Blake2b core is able to generate a new hash output after an initial delay of 2 + ceil(input bytes/128)\*24, so for the solution checker here (140B input, 512 hashes), we achieve 177M hash/s. Maximum performance would be at 5G hash/s.

### Performance evaluation

#### **FPGA** resources

### Percentages reported for the VU37P

| LUT        | FF         | DSP | BRAM     |

|------------|------------|-----|----------|

| 87914 (3%) | 54362 (3%) | 0   | 6 (0.2%) |

#### Clock cycles

|                   | FPGA clock cycles | FPGA throughput | CPU cycles | 3GHz CPU throughput |

|-------------------|-------------------|-----------------|------------|---------------------|

| Solution check    | 600 @100MHz       |                 |            |                     |

| Index order check | 356 @100MHz       |                 |            |                     |

| Duplicate check   | 1443 @300MHz      |                 |            |                     |

| Difficulty check               | 1068 @300MHz |           |          |          |

|--------------------------------|--------------|-----------|----------|----------|

| Equihash solution verification | 1068 @300MHz | 207K op/s | ~2868040 | ~1K op/s |

Here performance on FPGA is 207X faster, likely due to high performance Blake2b core, as well as all checks being done in parallel.

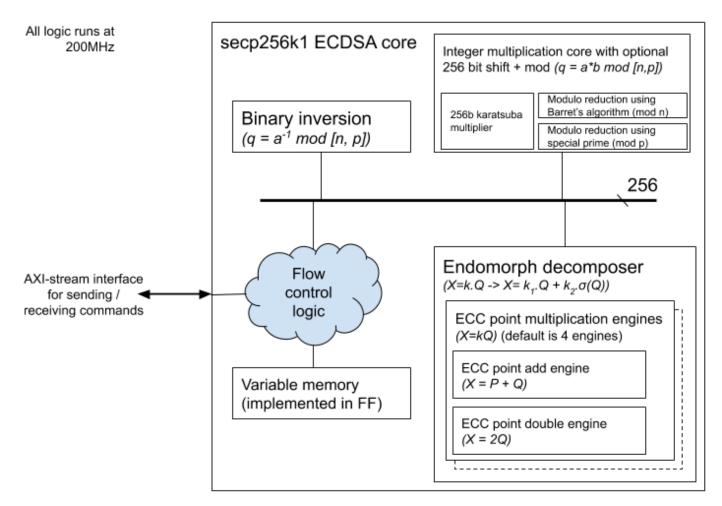

# Transparent Signature Verification Engine (secp256k1 ECDSA core)

### Overview

This engine handles all the operations for the curve secp256k1. This block at a top level supports point multiplication with a top level state controller, point multiplication, point addition, point doubling, point inversion, integer multiplication, and integer modulo reduction blocks. Blocks are shared via a resource arbitrator. We optionally can use the endomorphism of secp256k1 to split the k in X=kQ into two smaller half-size k1 and k2, by instantiating a "endomorphism decom block", which gives close to a 2x improvement in throughput, at the cost of having 2 more multiplication engines.

We create two ECC point multiplication modules which run in parallel to calculate  $X = u_1P + u_2Q$  required for signature verification. These run in parallel, but due to the pipelined integer multiplication core we have both point multiplication modules share this.

The algorithm used for point multiplication is the double and add method, but we take advantage of the FPGA parallelism and do the double and add at the same time. Since doubling is faster than adding, we start the next double if we have an unfinished add in progress, improving performance. Each point double takes 54 clock cycles and each point addition takes 104 clock cycles.

The integer multiplication core is implemented with the karatsuba algorithm (2 levels) and each level is pipelined over 3 flip-flops (for timing @ 200MHz), so that a result is valid after 6 clock cycles, with a new result every clock cycle. On the output we can optionally bit shift (used for endomorph decomposition), reduce the result mod p (taking 2 clock cycles as it takes advantage of the prime form), or reduce the result mod n which takes longer as it uses barrett's algorithm. Mod n operations are only required at the start and very end so this path does not need to be optimized too much.

Binary inversion uses the gcd algorithm and takes roughly 708 clock cycles, so this is avoided as much as possible by: 1) Converting to jacobian coordinates for point multiplication and 2) the signature result can be checked without converting back to affine coordinates using the same method as in Zcash's git source code.

### Performance evaluation

Average performance of the core is shown below for signature verification (which will depend on the number of adds/doubles required). This is also compared to the same function from zcash's git running on a 3GHz processor (measured using average of CPU cycle counts). I did not try to optimize by using non-adjacent form . (NAF) window methods / Shamir's trick, as on the FPGA we run the calculations truly in parallel and might not benefit from these techniques, although this could be a point for future exploration. Improving the equations used for point double and point add would also improve performance. The FPGA was successfully meeting timing at a 200MHz clock. FPGA throughput could be improved by instantiating more cores.

#### **FPGA** resources

#### Percentages reported for the VU37P

|                                                  | LUT          | FF           | DSP        | BRAM     |

|--------------------------------------------------|--------------|--------------|------------|----------|

| secp256k1 ECDSA core (without endomorph enabled) | 57697 (4.4%) | 31751 (1.2%) | 144 (1.6%) | 2 (0.1%) |

| secp256k1 ECDSA core (with endomorph enabled)    | 98792 (7.5%) | 61909 (2.1%) | 144 (1.6%) | 2 (0.1%) |

#### Clock cycles

| FPG/ | A clock cycles | FPGA throughput | CPU cycles | 3GHz CPU |

|------|----------------|-----------------|------------|----------|

|------|----------------|-----------------|------------|----------|

|                                                  |        |                 |         | throughput  |

|--------------------------------------------------|--------|-----------------|---------|-------------|

| Point double mod p                               | 54     | 3.7M op/s       |         |             |

| Point add mod p                                  | 104    | 1.9M op/s       |         |             |

| Inversion mod n                                  | 708    | 282K op/s       |         |             |

| secp256k1 ECDSA core (without endomorph enabled) | ~20224 | ~9.9K op/s/core | ~223350 | ~13.4K op/s |

| secp256k1 ECDSA core (endomorph enabled)         | ~10100 | ~20K op/s/core  |         |             |

FPGA performance is 1.5X compared to a 3GHz CPU. The FPGA could instantiate multiple ECC engines to run in parallel.

Comparison to other FPGA work

This will be added in a future release

### **Future Optimizations**

Investigating the impact using NAF has on performance would be the next possible optimization.

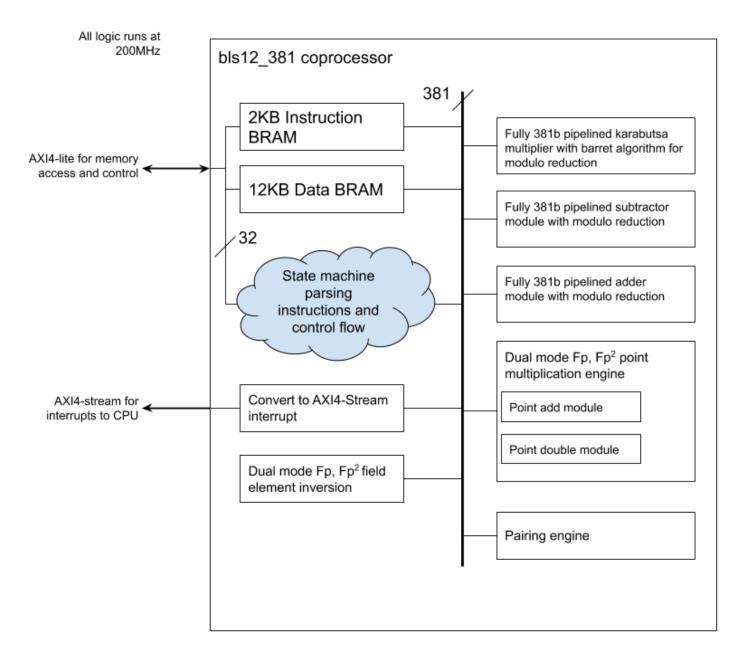

## BLS12-381 Coprocessor (zk-SNARK accelerator)

### Overview

This coprocessor is used to accelerate zk-SNARKS as the majority of elliptical arithmetic used during proving and verifying is run on top of the bls12-381 curve.

Unlike previous cores, the coprocessor can be configured by writing to instruction memory rather than accepted hard coded commands. This is to allow more flexibility in how the co-processor is used. SW can either poll registers on the FPGA coprocessor or use interrupt instructions so that the FPGA will send data to SW.

The coprocessor has instruction memory that can be written to, after a reset command the entire memory is initialized to NOOP-WAIT. The coprocessor has a memory bank with addressable data slots each 64 bytes wide per address for variables that can be used with instructions, example sizes for variables are:

- Scalar integer takes 1 slot

- Point in Fp takes 3 in jacobian coordinates (2 in affine)

- Point in Fp<sup>2</sup> take 6 in jacobian coordinates (4 in affine)

- Fp<sup>12</sup> element takes 12 slots

Each data slot only uses 48 bytes on the FPGA (64 bytes of address space is used in SW to simplify the mapping of memory to slot index). The first 381 bits of a slot store that elements data, the remaining 3 bits are used as a format for the type of element stored (more bits can be added if needed).

| 0 | Scalar     |

|---|------------|

| 1 | Fp element |

| 2 | Fp <sup>2</sup> element  |

|---|--------------------------|

| 3 | Fp <sup>12</sup> element |

| 4 | Fp point AF              |

| 5 | Fp point JB              |

| 6 | Fp <sup>2</sup> point AF |

| 7 | Fp <sup>2</sup> point JB |

### Instructions

Instructions are 8 bytes each (1 byte for op-code, and then the rest is used to address variables).

Interrupts are sent by using the SEND-INTERRUPT instruction which can be used to send the result of a calculation to SW. SW will have a method of registering a callback function that would be called when an interrupt is detected, the function will take a pointer to memory that will hold the data sent from FPGA.

Montgomery form is not used in any of the operations (as we can use barret reduction with only +1 bits in the multiplier to keep the architecture simpler).

All point operations can be given inputs in affine or jacobian coordinates, but outputs will be in JB unless otherwise stated. There is not a specific instruction for converting to affine coordinates because you can get the same result by multiplying the point element (Fp or Fp<sup>2</sup>) by INV-ELEMENT(MUL-ELEMENT(Z, Z)).

Do not use the same slot location for input and output as for some commands this will corrupt the result. Instructions highlighted in grey have not been implemented yet and are planned for future releases.

| Instruction                 | Description                                                                                                                                                                                                                                    |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOOP_WAIT (0x0)             | Coprocessor waits at this command and does nothing (used to stall or after a reset)                                                                                                                                                            |

| COPY_REG(0x1, a, b)         | Copy contents of register b = a                                                                                                                                                                                                                |

| JUMP(0x2, a)                | Jump instruction pointer to location a                                                                                                                                                                                                         |

| JUMP_ZERO(0x3, a, b)        | Jump instruction pointer to location a if b == 0                                                                                                                                                                                               |

| JUMP_EQ(0x4, a, b, c)       | Jump instruction pointer to location a if b == c                                                                                                                                                                                               |

| JUMP_NONZERO-SUB(0x5, a, b) | If b != 0 then jump to a and b, otherwise continue                                                                                                                                                                                             |

| SEND_INTERRUPT(0x6, a, b)   | Send an interrupt to SW along with the data in slot a. Amount of bytes sent will depend on data type stored in slot. 16 bit value of b will be appended to the interrupt message header (see streaming commands for bls12_381_interrupt_rpl_t) |

|                             |                                                                                                                                                                                                                                                |

| MUL-ELEMENT (0x10, a, b, c)              | Do Fp / Fp <sup>2</sup> field element multiplication, $c = a \times b$                                                                                 |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD-ELEMENT (0x11, a, b, c)              | Do Fp / Fp <sup>2</sup> field element addition, $c = a + b$                                                                                            |

| SUB-ELEMENT (0x12, a, b, c)              | Do Fp / Fp <sup>2</sup> field element subtraction, $c = a - b$                                                                                         |

| INV-ELEMENT(0x13, a, b)                  | Calculate the inverse of a Fp / Fp <sup>2</sup> field element a and store in b                                                                         |

|                                          |                                                                                                                                                        |

| POINT_NEG(0x20, a, b)                    | Negate a Fp / Fp <sup>2</sup> point in a and store result point in b. $b = -a$                                                                         |

| POINT_ADD(0x21, a, b, c)                 | Do a point addition using Fp / $Fp^2$ points a and b, and store result jacobian point in c. c = a + b                                                  |

| POINT_DBL(0x21, a, b, c)                 | Do a point double using Fp / $Fp^2$ points a and b, and store result jacobian point in c. c = a + b                                                    |

| POINT_MULT(0x22, a, b, c)                | Do a Fp / Fp <sup>2</sup> point multiplication using scalar a and Fp / Fp <sup>2</sup> point b, and store result jacobian point in c. $c = a \times b$ |

| <sup>1</sup> FP_FPOINT_MULT(0x23, a, b)  | Do a fixed Fp point multiplication using scalar a and Fp generator point, and store result jacobian point in b. $b = a \times G$                       |

| <sup>1</sup> FP2_FPOINT_MULT(0x24, a, b) | Do a fixed $Fp^2$ point multiplication using scalar a and $Fp^2$ generator point, and store result jacobian point in b. b = a x G                      |

| PAIRING(0x28, a, b, c)                   | Do a ate pairing of the G1 Fp point in a and G2 $Fp^2$ point in b, and store result $Fp^{12}$ field element in c                                       |

|                                          |                                                                                                                                                        |

### Notes:

<sup>1</sup>Currently the FPOINT instructions do not use pre calculated values, but this can be changed to improve performance in a future version.

### Memory Map

This is the AXI-lite portion of the core that can be used for configuration, as well as writing/reading instruction/data memory.

| Register Name                             | Address | Access                                                                                                                                                                        |  |  |  |  |  |  |  |

|-------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Instruction memory offset / reset control | 0x0     | Read: returns the memory offset where instruction<br>memory begins<br>Write: A '1' to bit[0] will reset the instruction memory, a '1'<br>to bit[1] will reset the data memory |  |  |  |  |  |  |  |

| Data memory offset                        | 0x4     | Read only: returns the memory offset where data memory begins                                                                                                                 |  |  |  |  |  |  |  |

| Data memory size             | 0x8  | Read only: returns the power of 2 number of data memory slots (i.e. 8 => 256 slots)                                                            |

|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction memory size      | 0xc  | Read only: returns the power of 2 number of instruction memory slots                                                                           |

| Current instruction pointer  | 0x10 | Read: returns current instruction memory pointer<br>Write: sets the instruction memory pointer (will wait until<br>current operation finishes) |

| Last instruction cycle count | 0x14 | Read only: returns the number of clock cycles the last instruction took to complete                                                            |

### Architecture

The coprocessor operates on a shared 381 bit bus with a main state machine with pointers into a data and instruction memory (implemented using Xilinx Ultra RAM on the FPGA). The top level multiplier, adder, and subtractor are all fully pipelined (so a new result each clock) and are resource shared with the entire coprocessor (so inversion block, dual mode point multiplier, pairing engine,... all use this).

The entire coprocessor uses parameterized values and modulo reduction is done via Barrets algorithm, so could easily be adapted to other curves with minimal effort.

Due to bls12-381 not having a hardware-friendly modulus (such as a Mersenne prime) the bulk of performance (66%+) is consumed by the multiplication reduction algorithm. For example at 381 bits we use a three stage karabutsa multiplier, which has 3 pipeline stages per logic stage. So a 381 multiplication takes 9 clock cycles, but then the following reduction with Barrets algorithm takes a further 2 multiplications + shifts, so we end up adding 18+ clock cycles.

#### Performance Comparison

#### **FPGA** resources

#### Percentages reported for the VU37P

| LUT | FF | BRAM |  |

|-----|----|------|--|

|     |    |      |  |

#### Clock cycles

Here performance was benchmarked vs the Rust bls12\_381 crate on a 32GB, 3.7GHz i5-9600K CPU. FPGA is running at 200MHz.

|                                                   | FPGA clock cycles | FPGA throughput | 3GHz CPU throughput |

|---------------------------------------------------|-------------------|-----------------|---------------------|

| Fp element inversion                              |                   |                 |                     |

| Fp <sup>2</sup> element inversion                 |                   |                 |                     |

| Fp multiplication + modulo reduction              |                   |                 |                     |

| Fp <sup>2</sup> multiplication + modulo reduction |                   |                 |                     |

| Fp point multiplication                           | 71148             | 2808 (op/s)     | 4926 (op/s)         |

| Fp <sup>2</sup> point multiplication              | 88664             | 2257 (op/s)     | 1499 (op/s)         |

|                                                   |                   |                 |                     |

Comparison to other FPGA work This will be added in a future release eg: https://eprint.iacr.org/2016/569.pdf

### **Future Optimizations**

Investigating the impact of NAF on point multiplication, as well as pre-computation for the double / add values used in the miller loop over  $Fp^2$ .

# User Guide

This section goes over example usage of the system.

# **Running Simulations**

## Module level simulations

Most modules have a corresponding "\_tb.sv" in the tb/ folder, and are self checking so can be added to local copy of Vivado and ran, and will print a message that all tests passed for that module if there are no problems. A top level simulation that tests all functions and emulates the Bittware VVH top level is here <u>https://github.com/bsdevlin/zcash-fpga/blob/master/zcash\_fpga/src/tb/zcash\_fpga\_top\_tb.sv</u>

# AWS Board level

The simulation test cases for the AWS board are in the repo folder

https://github.com/bsdevlin/zcash-fpga/tree/master/aws/cl\_zcash/verif/tests and can be run by:

- 1. cd /home/centos/aws-fpga/hdk/cl/developer\_designs/cl\_zcash/verif/scripts

- 2. make all

This will compile the test cases and then run them, they are all self checking, so if not ERRORs are printed and the simulation finishes then there are no problems. If something unexpected happens you can run xsim and look at the waveforms.

# Usage with a local FPGA board

If the board is local, it can be configured over USB-UART (note this is very low bandwidth and just mainly used for proof of concept / testing).

Commands can be called from the python script: bittware\_xupvvh/software/zcash\_fpga.py

# Usage on AWS

AWS runs over PCIe and has a higher bandwidth, but due to timing a slower clock is used (as there is more glue logic on the FPGA).

At the time of writing this these were the versions used in the AWS toolchain:

| Developer Kit | Tool Version       | Compatible FPGA developer AMI |

|---------------|--------------------|-------------------------------|

| Version (HDK) | Supported (Vivado) | Version                       |

| 1.4.8-1.4.X   | 2018.3             | v1.6.0 (Xilinx SDx 2018.3)    |

# Building the FPGA image

If you make changes to the code or want to build a new image, you can follow the steps below. If you do not want to do this, you can skip to the next section "Loading FPGA image" and use one of the pre-built images listed in "Existing AFIs".

- Start an AWS instance and load it with the FPGA Developer AMI (<u>https://aws.amazon.com/marketplace/pp/B06VVYBLZZ</u>)

- a. This should be a f1 instance (e.g. f1.2xlarge) so you have access to an FPGA

- b. If you just want to build the FPGA image you can use a cheaper instance like r5.xlarge (just need at least 32GB RAM)

- 2. Clone the zcash git repo

- 3. Clone the aws-fpga repo

- a. git clone https://github.com/aws/aws-fpga.git

- Copy the folder zcash-fpga/aws/cl\_zcash to the AWS folder

- a. cp -r /home/centos/zcash-fpga/aws/cl\_zcash /home/centos/aws-fpga/hdk/cl/developer\_designs/

- 5. Copy the folder /home/centos/aws-fpga/hdk/cl/examples/common

- a. cp -r /home/centos/aws-fpga/hdk/cl/examples/common /home/centos/aws-fpga/hdk/cl/developer\_designs/

- 6. Run the hdk\_source.sh script to setup the AWS environment

- a. cd /home/centos/aws-fpga; source hdk\_setup.sh

- b. Note: If you get an error with Vivado not being present, it might be due to locale issue, try:

- i. export LC\_ALL="en\_US.UTF-8"

- 7. Set the variables for Zcash scripts:

- a. export CL\_DIR=/home/centos/aws-fpga/hdk/cl/developer\_designs/cl\_zcash; export ZCASH\_DIR=/home/centos/zcash-fpga/

- 8. Generate the FPGA IP files

- a. cd /home/centos/aws-fpga/hdk/cl/developer\_designs/cl\_zcash/ip/; ./run\_cl\_sde\_ip\_flow

- 9. Start building the FPGA image

- a. cd /home/centos/aws-fpga/hdk/cl/developer\_designs/cl\_zcash/build/scripts ; ./aws\_build\_dcp\_from\_cl.sh -clock\_recipe\_a A0 -clock\_recipe\_b B1

- Note: AWS clock recipes are here: <u>https://github.com/aws/aws-fpga/blob/master/hdk/docs/clock\_recipes.csv</u>, a higher performance version of the core can use "-clock\_recipe\_a A1 -clock\_recipe\_b B0", a slower version (but easier to build and meet timing) could use "-clock\_recipe\_a A2 -clock\_recipe\_b B1 -strategy BASIC"

- i. Note: this will not work with an ILA debug core since the clock speed (15MHz) is too slow compared to JTAG frequency

- c. You can check progress by looking at "/home/centos/aws-fpga/hdk/cl/developer\_designs/cl\_zcash/build/scripts/last\_log"

The build should run and will take several hours, depending on the instance type / clock recipe. If there are no problems, the output will be in

/home/centos/aws-fpga/hdk/cl/developer\_designs/*cl\_zcash*/build/checkpoints/to\_aws/\*.tar and needs to be uploaded to an Amazon S3 bucket. The bucket used in this project is "zcash-fpga-west". From here you can follow the standard flow detailed on the AWS FPGA github:

https://github.com/aws/aws-fpga/blob/master/hdk/README.md#step3 .

After this you should have an agfi-ID that can be used to program the FPGA.

## Loading FPGA image

To load an FPGA image you need it's agfi-ID, either from the previous step or from the table in the following section "Existing AFIs".

Run this commands to load the FPGA:

1. sudo fpga-load-local-image -S 0 -I -F agfi-ID

**Note**: You can check for errors / metrics by running the command "sudo fpga-describe-local-image -S 0 --metrics". If you see all 0's then there is no problem, but if you see some timeouts like this:

ocl-slave-timeout-addr=0x2001 ocl-slave-timeout-count=4

You should reload the FPGA image (step 1 above). There is a known issue with AWS where the first load will sometimes show this problem, but reloading FPGA fixes it.

## Rust interface

A rust interface has been developed to allow the Zcash client to utilize the FPGA acceleration.

## Startup test program

A simple program is in /home/centos/aws-fpga/hdk/cl/developer\_designs/*cl\_zcash*/software/runtime/ (test\_zcash)

- 1. Run the sdk\_source.sh script to setup the software AWS environment

- a. cd /home/centos/aws-fpga; source sdk\_setup.sh

Run the make file and then the test program (using sudo), and check there are no errors. Expected output would be this:

This will be added in a future release

# FPGA debug

Debug instructions can be found here:

<u>https://github.com/aws/aws-fpga/blob/master/hdk/docs/Virtual\_JTAG\_XVC.md</u> There is a parameter in cl\_zcash.sv, USE\_ILA = "NO" which can be changed to "YES" to enable a build with the debug logic. You can change the connections as needed.

# **Existing AFIs**

These are the AFIs that already exist that can be used for testing / using the Zcash FPGA image on AWS. Version is tracked in the top level package zcash\_fpga\_pkg.sv

| agfi-ID                | afi-ID                | Notes                                                                                                                           |

|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| agfi-0528daff45454ed7c | afi-09056704c94b5280b | v1.0.0 First test version used for testing AWS flow, will not work with test program.                                           |

| agfi-05561b352d56b5f57 | afi-0c8109482d730073c | v1.0.1 Test version                                                                                                             |

| agfi-0fa84678db6b2752f | afi-07ec21206df23e398 | v1.1.0, Has all modules enabled but on a slow<br>clock recipe for testing. BLS12_381 core has Fp<br>and Fp2 fpoint instructions |

| agfi-019c2736fd0141219 | afi-0b891a8fc9644f1a0 | v1.1.0_150, only has BLS coprocessor enabled but running at 125MHz, uses AXI4 as PCIe interface                                 |

| agfi-05468e41c302eb331 | afi-06a4b56d6e4bfd896 | v1.1.1, contains all cores @ 125MHz, uses AXI-lite as PCIe interface                                                            |

| agfi-0fce4c1ad9e0c6c43 | afi-0da67f631a2573656 | v1.1.2 contains all cores @ 125MHz                                                                                              |

| agfi-0c4a39d7638bc6010 | afi-0bcef9f0c08bee7c1 | v1.1.2 contains all cores @ 15MHz                                                                                               |

| agfi-0abc260b651d87d41 | afi-0075820f5d00bd799 | v1.1.3 Bug fixes to BLS12_381 core, 125MHz                                                                                      |

| agfi-07ae22f20d6e90559 | afi-0e49dd7ef17fda51a | v1.1.4, bug fix for multiple back to back interrupts, 125MHz                                                                    |

| agfi-0db37e1358c1d885f | afi-0907df570f7dc7b2b | Debug version of v1.1.4 above (15MHz)                                                                                           |

|                        |                       | v1.1.5, debug version 125MHz, BASIC flow                                                                                        |

# Conclusions

This will be added in a future release (project is still a work in progress)

# Appendix

# Example decoding Zcash block #346

### Hash 0x000000eff179fb1e47b7aa8667ad4d8e1ef3dbb0d79144030482bf93b5e6339f

Hex dump of block (CBlock):

| 0               | )4 | 00 | 00 | 00 | 13 | d6 | d1  | a4 | 10 | 51 | 42 | 19 | f7 | 2f | f3 | a0 | df | d5 | c3 | 8b | 62 | 1c | c2 | c6 | 68 | 78  | 4d | 2f | d6 | fd | 10       | 8f              |

|-----------------|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----------|-----------------|

| 20              | 48 | 00 |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    | cd | d9 | a9       | <mark>69</mark> |

| <mark>40</mark> | fb | 93 | 80 | 50 | 00 | 00 | 00  | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00  | 00 | 00 | 00 | 00 | 00       | 00              |

| <mark>60</mark> | 00 | 00 | 00 | 00 | 3f | 85 | 13  | 58 | bf | с3 | 03 | 1e | 1b | b2 | b5 | 50 | a4 | 01 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00  | 00 | 00 | 00 | 00 | 00       | 00              |

| <mark>80</mark> | 00 | 00 | 00 | 00 | 00 | 00 | 00  | 00 | 00 | 00 | 00 | 03 | fd | 40 | 05 | 00 | 9d | fa | 04 | 89 | e1 | 18 | 99 | dc | 5e | 50  | 5d | 91 | 24 | 57 | 44       | 49              |

| a0              |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | d4       |                 |

| c0              |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 6b       |                 |

| e0              |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 55       |                 |

| 100             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 15       |                 |

| 120             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 99       |                 |

| 140             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | b5       |                 |

| 160             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | db       |                 |

| 180             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 37       |                 |

| 1a0<br>1c0      |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | ba       |                 |

| 1e0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 8a<br>83 |                 |

| 200             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 03<br>23 |                 |

| 220             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | af       |                 |

| 240             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 8f       |                 |

| 260             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 71       |                 |

| 280             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | a4       |                 |

| 2a0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 99       |                 |

| 2c0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | b4       |                 |

| 2e0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 2c       |                 |

| 300             | :9 | ff | 91 | 35 | e2 | 20 | a3  | d9 | 33 | ff | 8d | fa | 2b | 24 | 61 | 12 | 93 | ad | ae | 45 | 99 | 76 | 1b | 2e | 0e | 32  | 2a | 36 | 7c | a3 | ea       | f5              |

| 320             | 44 | 33 | da | 78 | 95 | 27 | 53  | 6d | d5 | 6a | 26 | c7 | f9 | 5f | b7 | 01 | cf | 9e | 2f | 00 | 52 | 68 | 11 | 70 | fa | 95  | 50 | ad | 69 | bd | 5e       | 15              |

| 340             | £6 | 9c | 81 | 5f | 1b | с7 | f7  | 79 | fa | 18 | 30 | 47 | dd | 86 | f4 | 61 | b1 | a3 | e3 | 3b | 97 | ec | 3d | 59 | b3 | 17  | c4 | 8d | 36 | de | ba       | 7d              |

| 360             | Bd | fc | d6 | e3 | 71 | a8 | d9  | 32 | 1e | 7e | d7 | 79 | с0 | a4 | 44 | 66 | 44 | 16 | 15 | 2c | ad | f5 | e1 | 17 | 64 | ba  | f0 | 5f | 11 | 79 | cb       | 8f              |

| 380             | fa | 4c | 42 | 0a | d3 | 5f | b5  | d8 | f4 | 39 | 73 | b9 | с7 | 33 | da | e1 | e5 | 55 | 1a | 57 | 00 | 14 | fc | 03 | 4f | 8 0 | ff | 76 | 4c | 64 | b5       | e1              |

| 3a0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 8f       |                 |

| 3c0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 43       |                 |

| 3e0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 4f       |                 |

| 400             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 52       |                 |

| 420             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | ba       |                 |

| 440             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | d6       |                 |

| 460             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 35       |                 |

| 480<br>4a0      |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | d6<br>25 |                 |

| 4a0<br>4c0      |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 23<br>b4 |                 |

| 4e0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 50       |                 |

| 500             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | ae       |                 |

| 520             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 72       |                 |

| 540             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 38       |                 |

| 560             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | ca       |                 |

| 580             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | d2       |                 |

| 5a0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | cb       |                 |

| 5c0             |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    | 00       |                 |

| 5e0             | 00 | 00 | 00 | 00 | 00 | 00 | 00  | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | ff | ff | ff | ff | 04  | 02 | 5a | 01 | 00 | ff       | ff              |

| 600             | ff | ff | 02 | 20 | fa | 07 | 01  | 00 | 00 | 00 | 00 | 23 | 21 | 02 | 7a | 46 | eb | 51 | 35 | 88 | b0 | 1b | 37 | ea | 24 | 30  | 3f | 4b | 62 | 8a | fd       | 12              |

| 620             | cc | 20 | df | 78 | 9f | ed | e0  | 92 | 1e | 43 | ca | d3 | e8 | 75 | ac | 88 | fe | 41 | 00 | 00 | 00 | 00 | 00 | 17 | a9 | 14  | 7d | 46 | a7 | 30 | d3       | 1f              |

| 640             | 97 | b1 | 93 | 0d | 33 | 68 | a 9 | 67 | c3 | 09 | bd | 4d | 13 | 6a | 87 | 00 | 00 | 00 | 00 |    |    |    |    |    |    |     |    |    |    |    |          |                 |

#### Header:

Version:

04 00 00 00

Previous block hash:

13 d6 d1 a4 10 51 42 19 f7 2f f3 a0 df d5 c3 8b 62 1c c2 c6 68 78 4d 2f d6 fd 10 8f 48 00 00 00

#### Merkle Root hash:

| 30 | 16 | 31 | 55 | 23 | 12 | 34 | 90 |

|----|----|----|----|----|----|----|----|

| d5 | 3b | 6b | 9e | 23 | 1d | f8 | bo |

| b8 | c2 | d3 | 32 | 64 | сс | 02 | fS |

| cd | d9 | a9 | 69 | fb | 93 | 80 | 50 |

|    |    |    |    |    |    |    |    |

Final sapling root hash:

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00<

Time:

<mark>3f 85 13 58</mark>

Bits (Difficulty):

Nonce:

1b

b2

b5

50

a4

01

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

Equihash solution (the 0xfd4005 here is used to decode the length of the array of bytes, 0xfd means the size is stored as a 2 byte integer 0x4005 == 1344 bytes):

fd 40 05 .. 7b d5 db(1344 bytes until address 0x5ce)

#### **Transactions:**

Transaction input array size (one transaction):

01

Version (only 4 bytes here as is not overwinter):

Input to transaction array size (one input):

01

OutPoint:

Script (first byte is length, 4 bytes long):

Sequence:

Transaction output array size (two transactions):

1st transaction output amount (17300000, 0.173 ZEC):

1st transaction output script (first byte is length, 35 bytes long):

23 21 02 7a 46 eb 51 35 88 b0 1b 37 ea 24 30 3f 4b 62 8a fd 12 cc 20 df 78 9f ed e0 92 1e 43 ca d3 e8 75 ac

2nd transaction output amount (4325000, 0.04325 ZEC): 88 fe 41 00 00 00 00 00

2nd transaction output script (first byte is length, 23 bytes long):

| T / |    |    |    |    |    |    |    |

|-----|----|----|----|----|----|----|----|

| a 9 | 14 | 7d | 46 | a7 | 30 | d3 | 1f |

| 97  | b1 | 93 | 0d | 33 | 68 | a9 | 67 |

| с3  | 09 | bd | 4d | 13 | 6a | 87 |    |

Locktime: