Multi Voltage Safety Micro Processor Supply

TLF35584QVVS1 TLF35584QVVS2 TLF35584QKVS1 TLF35584QKVS2

# Data Sheet

Rev. 2.0, 2017-03-16

# Automotive Power

## **Table of Contents**

| 1   | Ove  | rview         |                                                                                  |

|-----|------|---------------|----------------------------------------------------------------------------------|

| 2   | Bloc | k Diagram     |                                                                                  |

| 3   | Pin  | Configurat    | ion                                                                              |

|     | 3.1  | Pin Ass       | ignment - PG-VQFN-48                                                             |

|     | 3.2  | Pin Def<br>8  | initions and Functions - PG-VQFN-48                                              |

|     | 3.3  | 13            | ignment - PG-LQFP-64                                                             |

| 4   | Gen  | eral Produ    | ct Characteristics                                                               |

|     | 4.1  |               | e Maximum Ratings                                                                |

|     | 4.2  | Functio       | nal Range                                                                        |

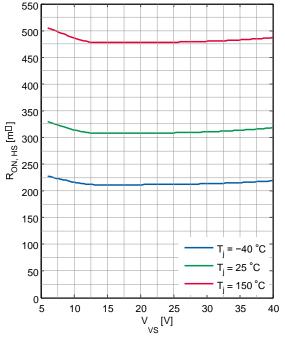

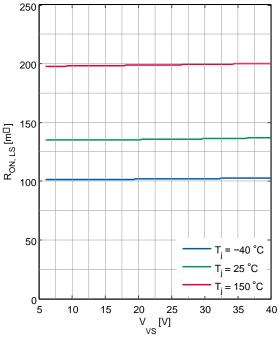

|     | 4.3  |               | I Resistance                                                                     |

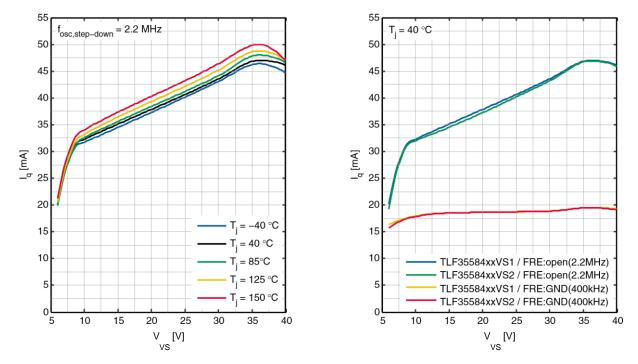

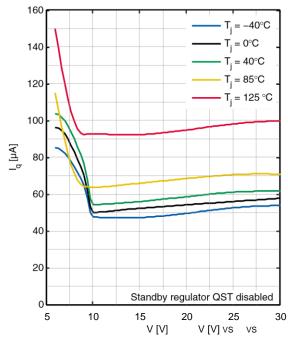

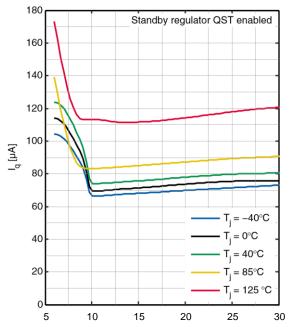

|     | 4.4  | -             | ent Current Consumption                                                          |

|     |      |               | I.4.1 Typical Performance Characteristics                                        |

|     |      |               | 25                                                                               |

| 5   | Wak  | e Function    |                                                                                  |

|     | 5.1  | Introduc      | xtion                                                                            |

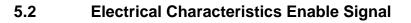

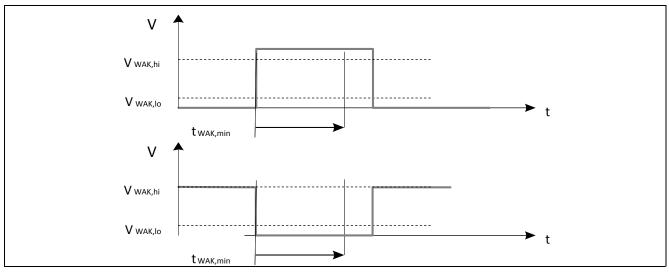

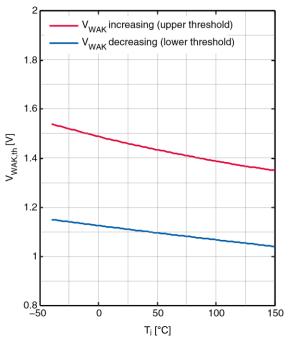

|     | 5.2  | 27 5          | al Characteristics Enable Signal      5.3 Electrical Characteristics Wake Signal |

| 5.4 | Tvn  |               | 28<br>nance Characteristics                                                      |

|     |      |               |                                                                                  |

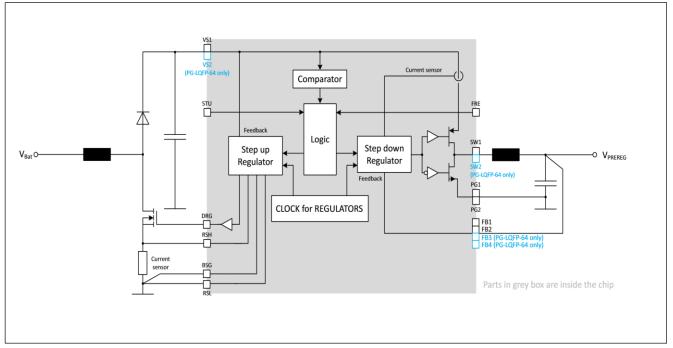

| 6   | 6.1  | •             |                                                                                  |

|     | 0.1  |               |                                                                                  |

|     | 6.2  | Step Up<br>31 | Regulator                                                                        |

|     |      | 6.2.1         | Functional description                                                           |

|     | 6.3  | Step Do       | wn Regulator                                                                     |

|     |      | 6.3.1         | Functional description                                                           |

|     |      | 6.3.2         | Electrical characteristics                                                       |

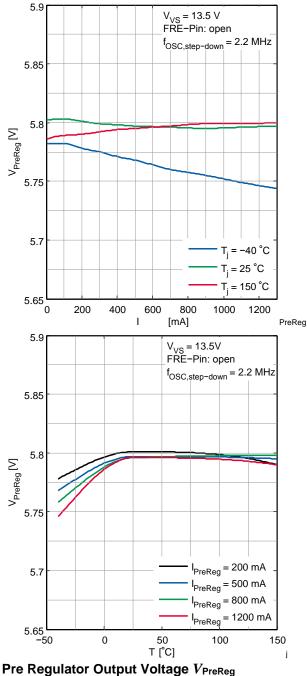

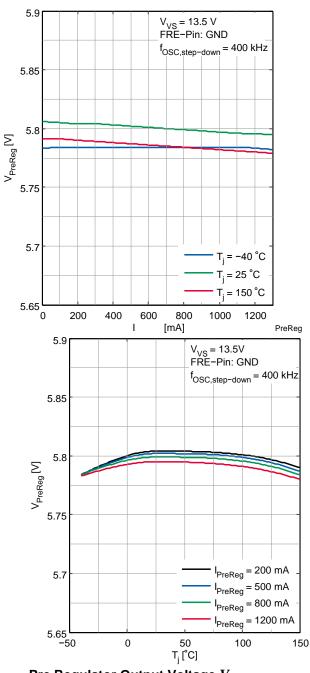

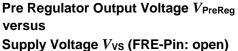

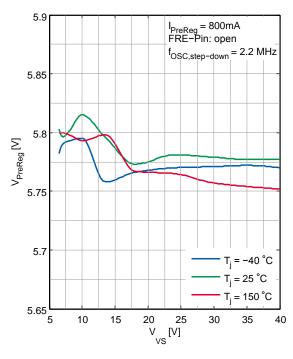

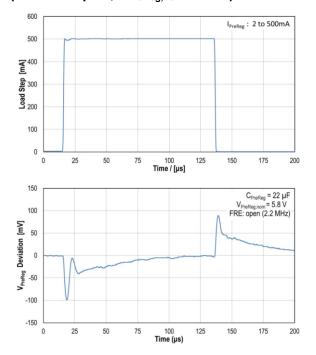

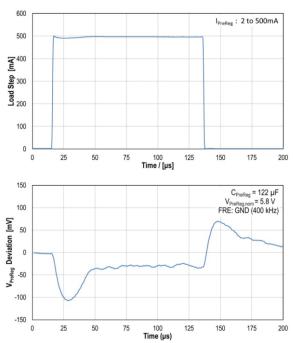

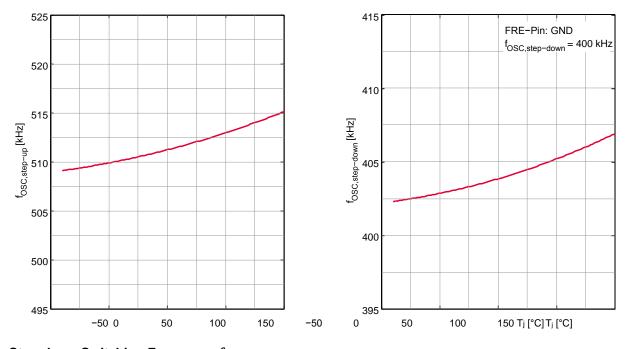

|     |      | 6.3.3         | Typical Performance Characteristics                                              |

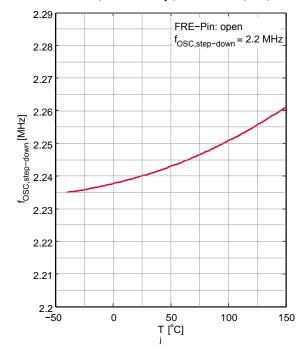

|     | 6.4  | Freque<br>39  | ncy setting                                                                      |

|   |       | 6.4.1       | Introduction                                 |

|---|-------|-------------|----------------------------------------------|

|   |       | 6.4.2       | Electrical characteristics frequency setting |

|   |       |             |                                              |

|   |       | 6.4.3       | Typical Performance Characteristics          |

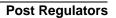

| 7 | Post  | Regulator   | s                                            |

|   | 7.1   | Introduc    | tion                                         |

|   | 7.2   | 43 7        | ssor Supply                                  |

|   | 7.2.2 |             | ical characteristics                         |

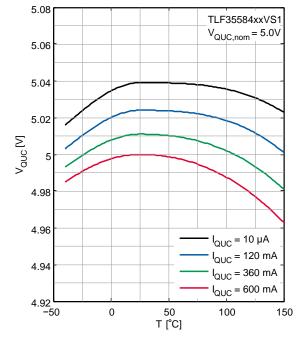

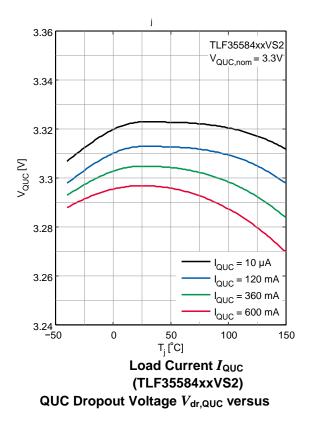

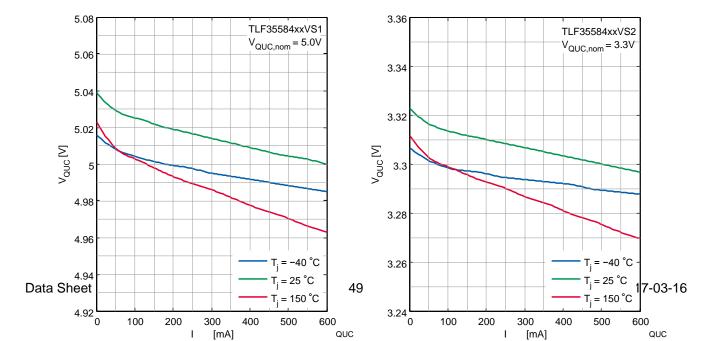

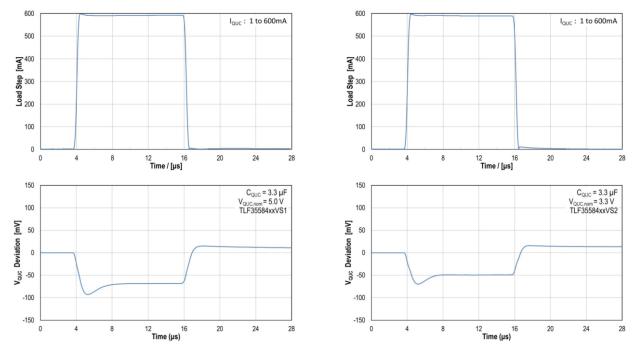

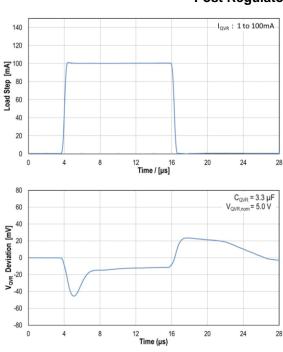

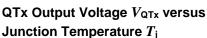

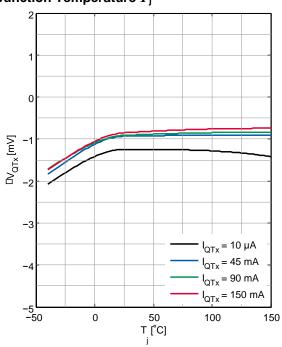

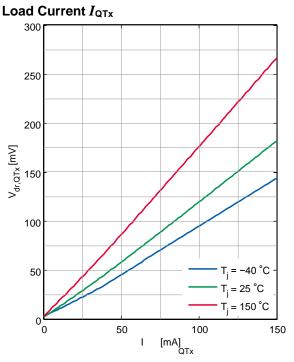

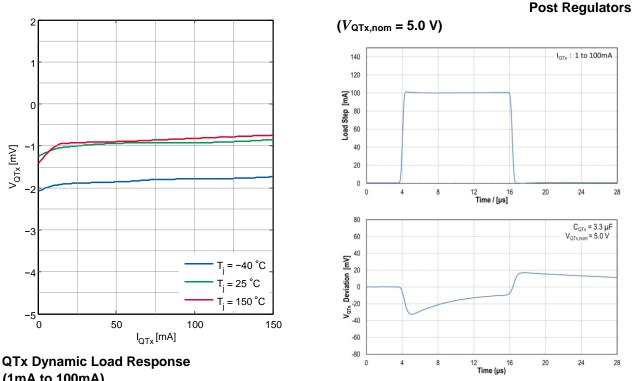

|   | 7.2.3 | Typica      | al Performance Characteristics               |

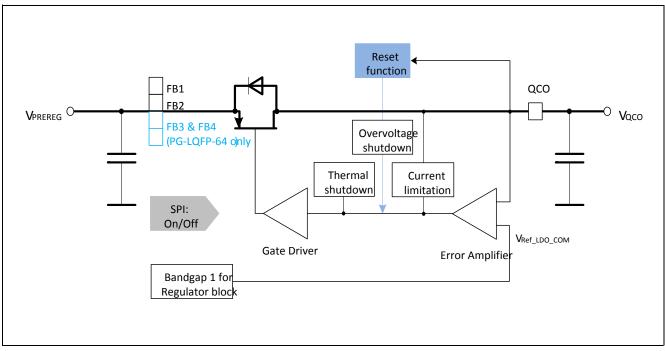

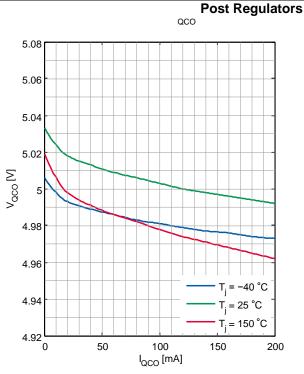

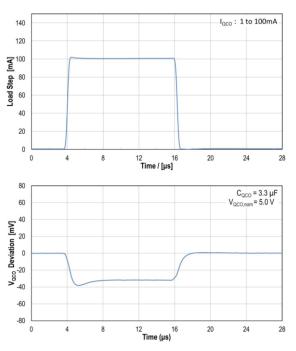

|   | 7.3   | Commu<br>49 | nication Supply                              |

|   |       | 7.3.1       | Functional description                       |

|   |       | 7.3.2       | Electrical characteristics                   |

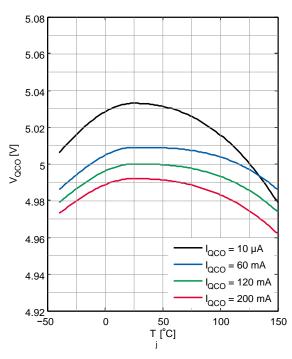

|   |       | 7.3.3       | Typical Performance Characteristics          |

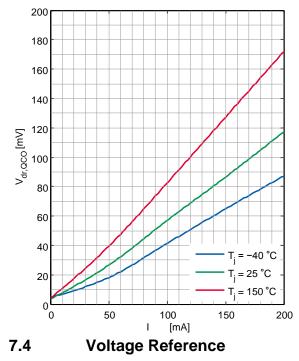

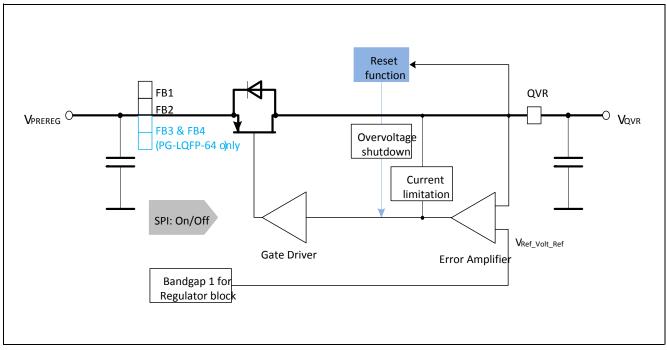

|   | 7.4   | Voltage     | Reference                                    |

|   |       | 7.4.1       | Functional description                       |

|   |       | 7.4.2       | Electrical characteristics                   |

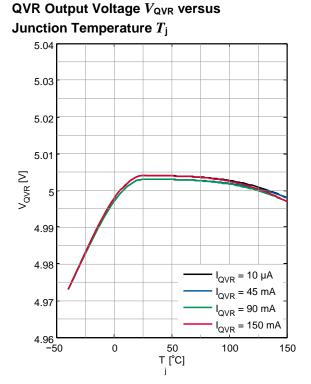

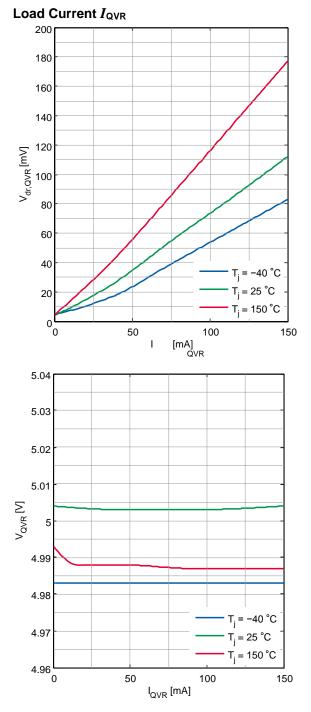

|   |       | 7.4.3       | Typical Performance Characteristics          |

|   | 7.5   | Tracker     | 1 & 2                                        |

|   |       | 7.5.1       | Functional description                       |

|   |       | 7.5.2       | Electrical characteristics                   |

|   |       | 7.5.3       | Typical Performance Characteristics          |

|   | 7.6   | Externa     | I Post Regulator for Core Supply (optional)  |

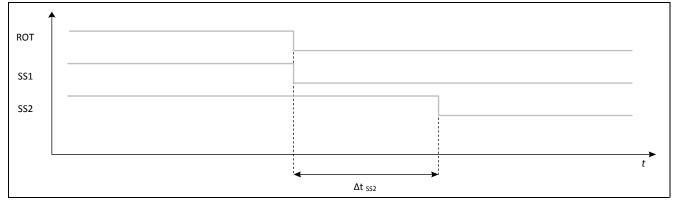

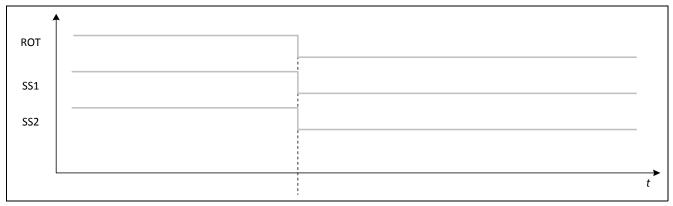

|   | 7.7   | Power \$    | Sequencing                                   |

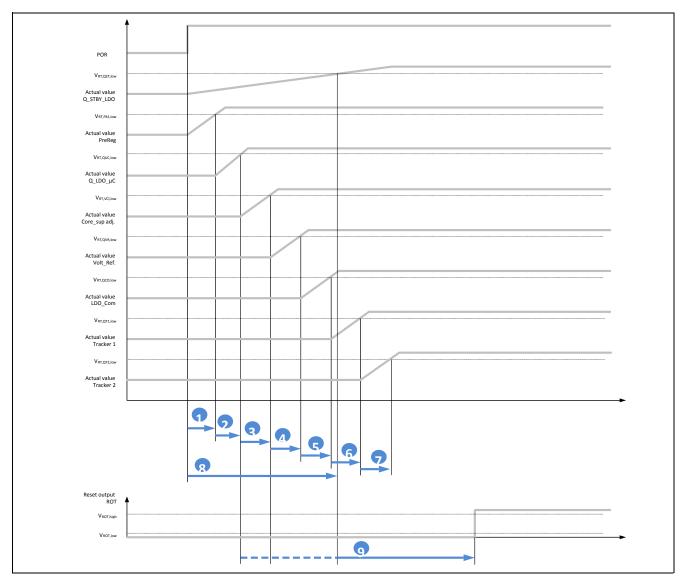

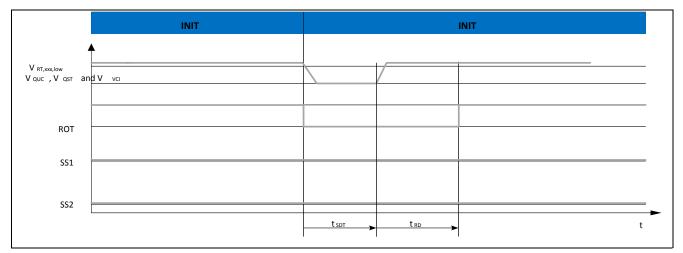

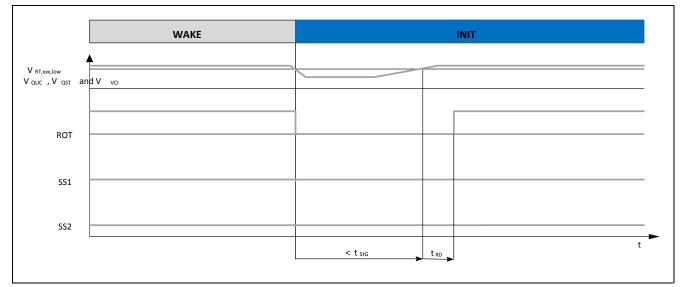

|   |       | 7.7.1       | Power sequencing from POR to INIT state      |

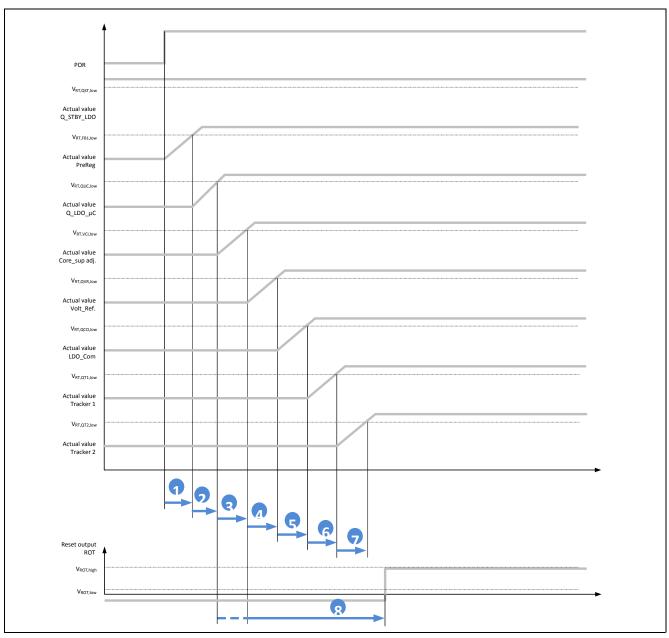

|   |       | 7.7.2       | Power sequencing STANDBY to INIT state       |

|   |       |             |                                              |

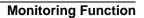

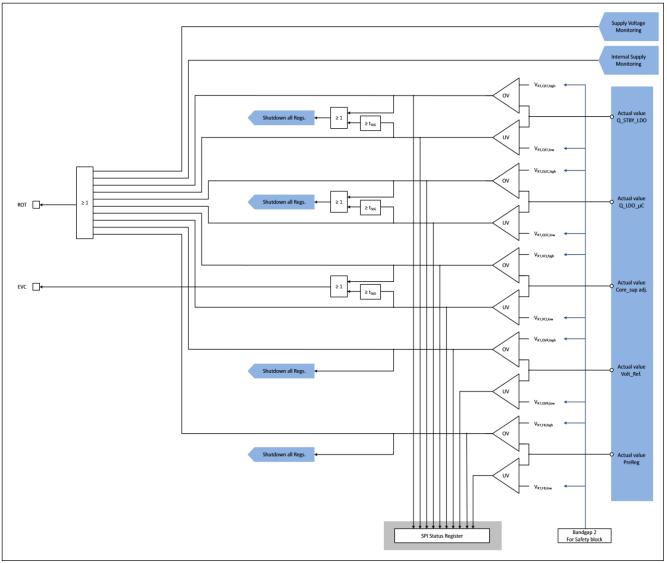

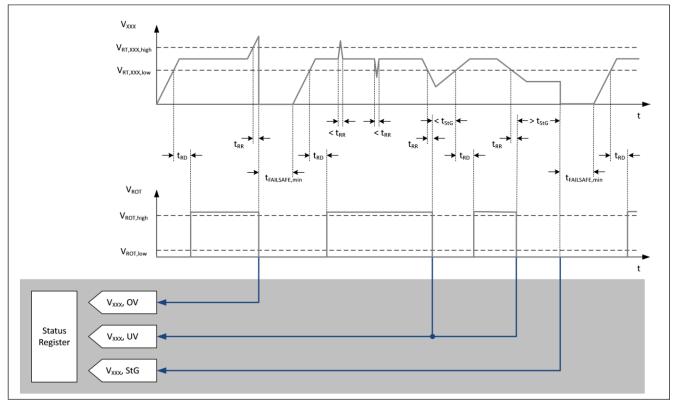

| 8      | Monit | oring Fund | ction                                    | 66    |

|--------|-------|------------|------------------------------------------|-------|

|        | 8.1   | Introduct  | ion                                      |       |

|        | 8.2   | Shutdow    | n Function                               |       |

|        | 8.3   |            | Inction                                  | •••   |

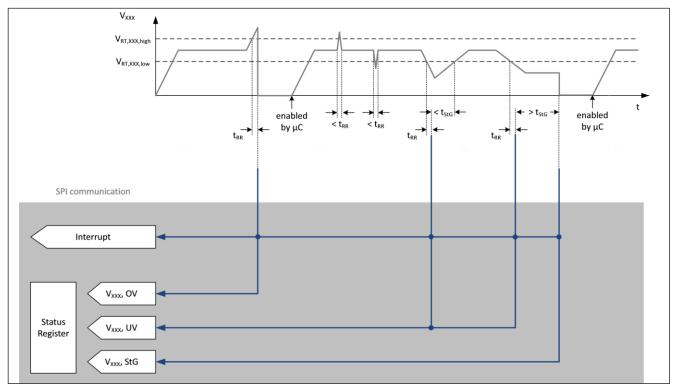

|        | 8.4   | Interrupt  | Function                                 |       |

|        |       |            | 73                                       |       |

| 9      | Stand | lby LDO ar | nd Internal Supplies                     | 77    |

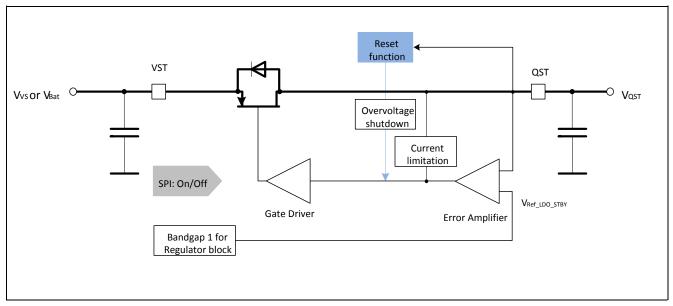

|        | 9.1   | Standby    | LDO:                                     |       |

|        |       | 9.1.1      | Functional description                   |       |

|        |       | 9.1.2      | Electrical characteristics               |       |

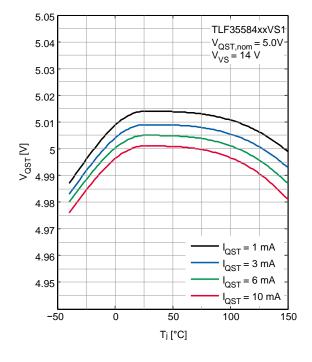

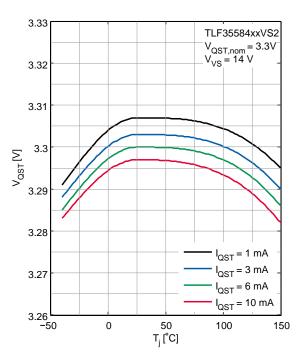

|        |       | 9.1.3      | Typical Performance Characteristics      |       |

|        |       |            |                                          |       |

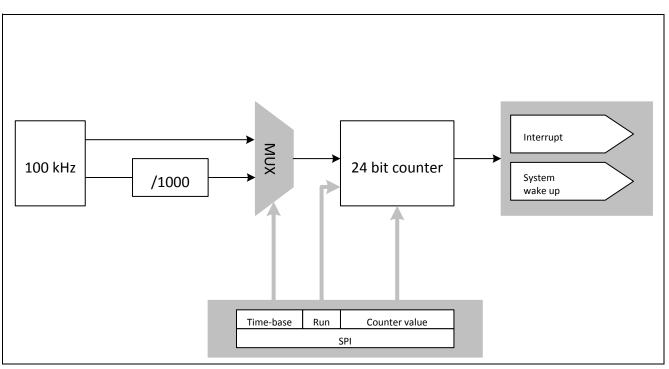

| 10     | Wake  | Up Timer   |                                          | 84    |

|        | 10.1  | Descripti  | on                                       |       |

|        |       |            | 0.2 Electrical Characteristics           |       |

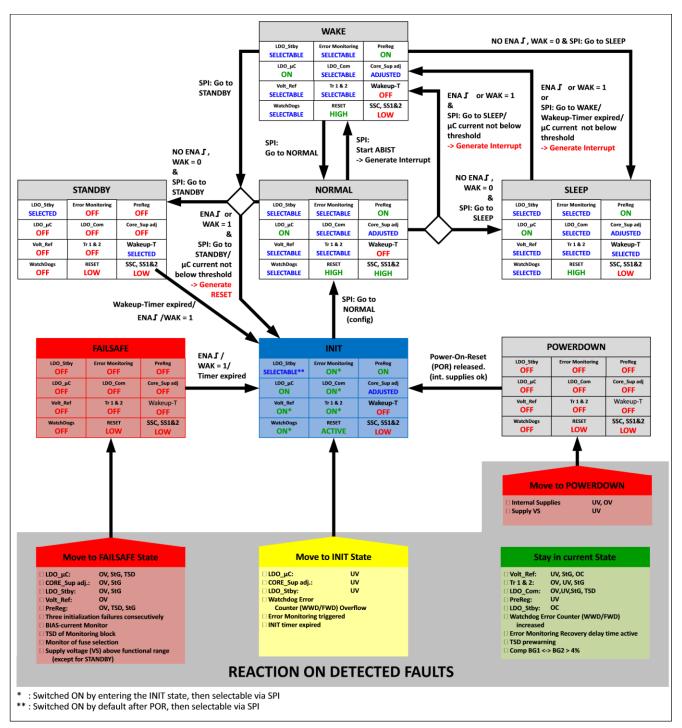

| 11     | State | Machine .  |                                          | 86    |

|        | 11.1  | Introduct  | ion                                      |       |

|        | 11.2  | Descripti  | on of States                             |       |

|        |       | 11.2.1     | POWERDOWN-state                          |       |

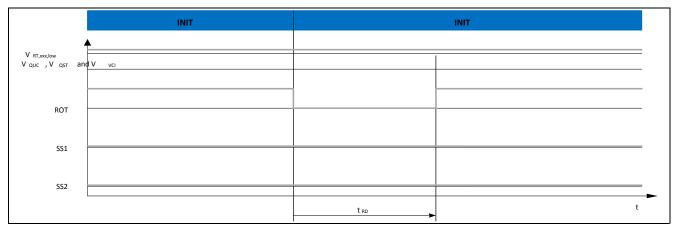

|        |       | 11.2.2     | INIT-state                               |       |

|        |       | 11.2.3     | NORMAL -state                            |       |

|        |       | 11.2.4     | STANDBY-state                            |       |

|        |       | 11.2.5     | SLEEP-state                              |       |

| 11.2.7 |       |            |                                          | 90    |

| 11.2.7 | 11.3  |            | n Between States                         |       |

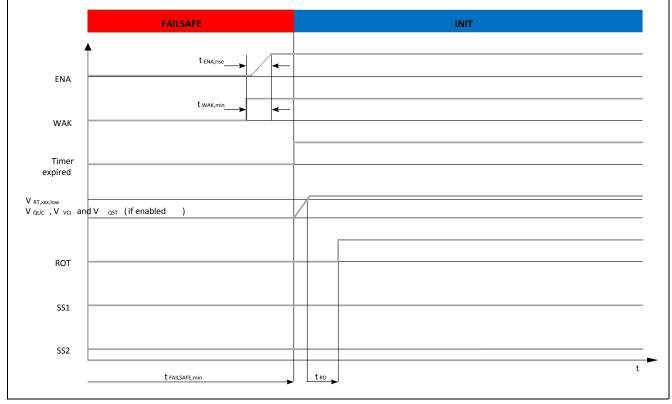

|        |       | 11.3.1     | POWERDOWN -> INIT-state                  |       |

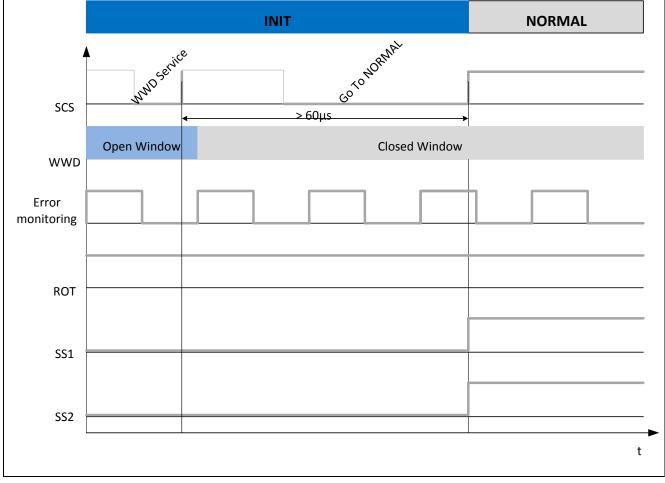

|        |       | 11.3.2     | INIT -> NORMAL-state                     | • • • |

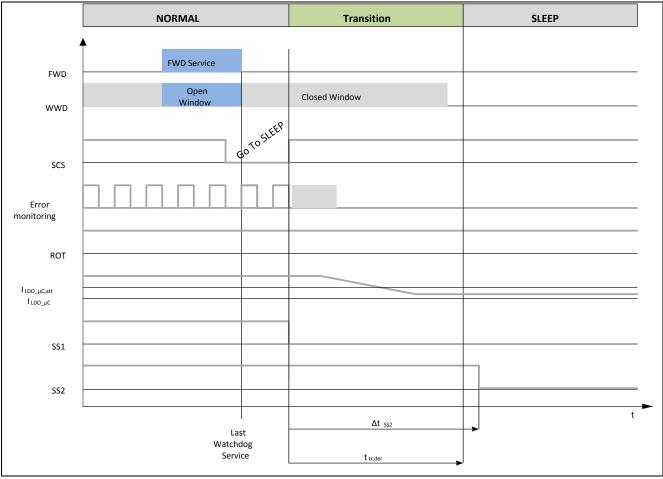

|        |       | 11.3.3     | Movements between NORMAL and SLEEP state |       |

|      |        | 11.3.3.1             | NORMAL -> SLEEP-state                                |

|------|--------|----------------------|------------------------------------------------------|

|      |        |                      |                                                      |

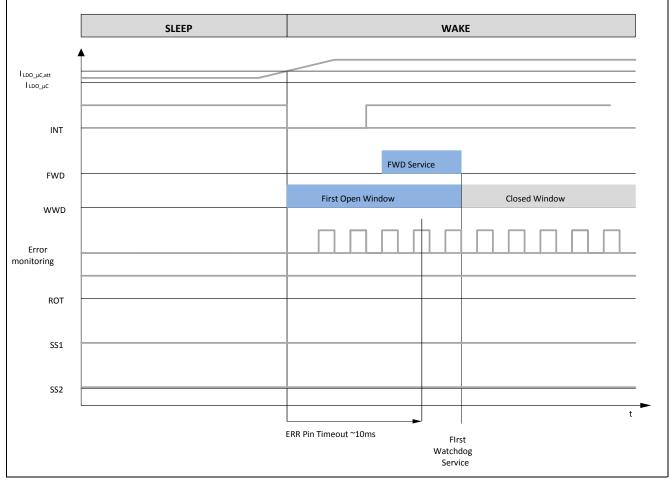

|      |        | 11.3.3.2             | SLEEP -> WAKE-state                                  |

|      |        |                      |                                                      |

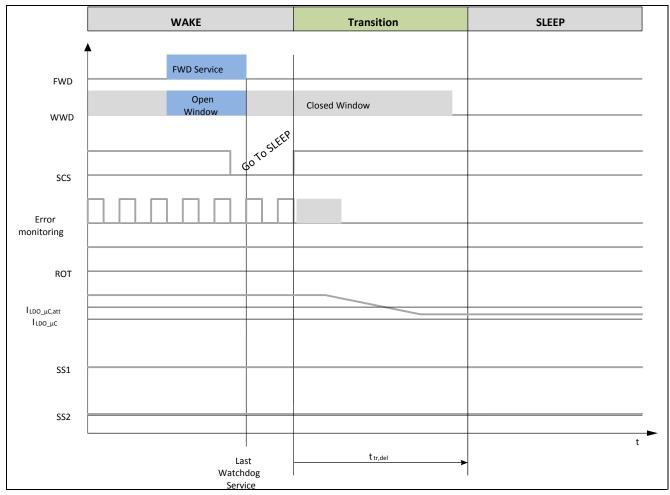

|      |        | 11.3.3.3             | WAKE -> SLEEP state                                  |

|      |        |                      |                                                      |

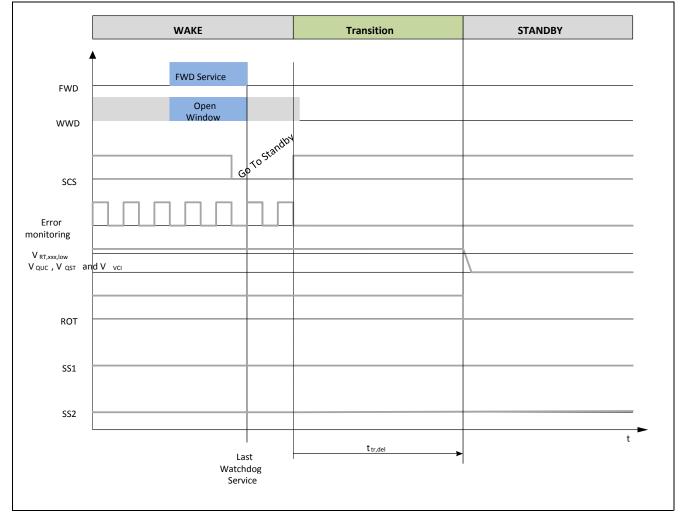

|      | 11.3.4 | Moveme               | nts between NORMAL and STANDBY state                 |

|      |        |                      |                                                      |

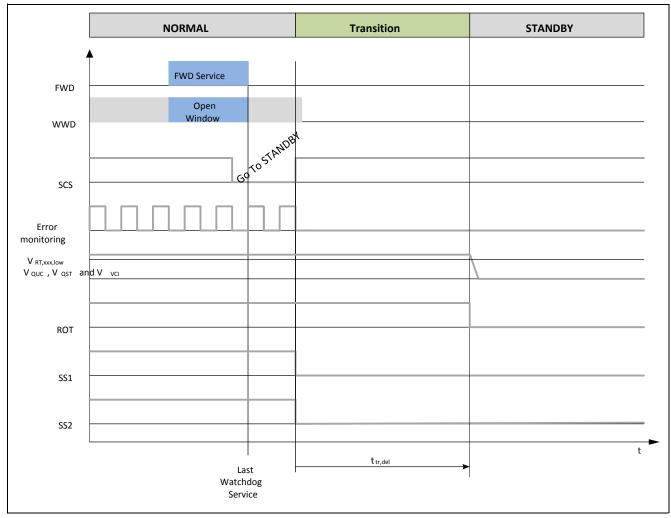

|      |        | 11.3.4.1             | NORMAL -> STANDBY-state                              |

|      |        | -                    |                                                      |

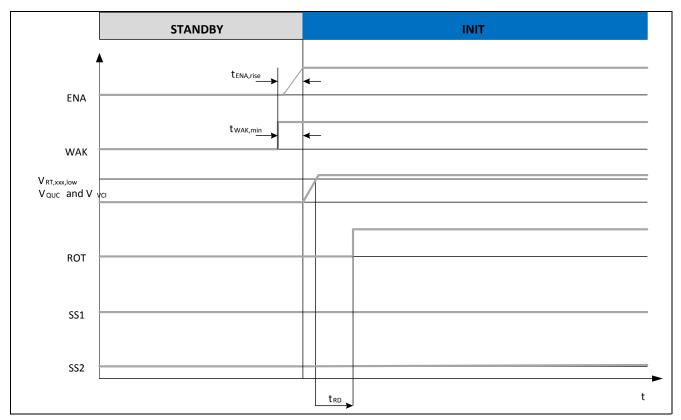

|      |        | 11.3.4.2             | STANDBY -> INIT state                                |

|      |        |                      |                                                      |

|      |        | 11.3.4.3             | INIT -> NORMAL state                                 |

|      | 11.3.5 | NORMAI               | L -> WAKE state                                      |

|      | 11.0.0 |                      |                                                      |

|      | 11.3.6 |                      | > NORMAL-state                                       |

|      | 11.3.0 | VVARE ->             |                                                      |

|      | 11.3.7 |                      |                                                      |

|      | 11.3.7 | VVARE ->             | • STANDBY state                                      |

|      | 44.0.0 |                      |                                                      |

|      | 11.3.8 |                      | E -> INIT state                                      |

|      | -      |                      |                                                      |

| 11.4 |        |                      | ed faults                                            |

|      | 119    |                      |                                                      |

|      | 11.4.1 |                      | urrent State                                         |

|      |        |                      | 119                                                  |

|      |        |                      |                                                      |

|      |        |                      |                                                      |

|      | 11.4.2 |                      | n into INIT State                                    |

|      |        |                      |                                                      |

|      |        | 11.4.2.1             |                                                      |

|      |        |                      |                                                      |

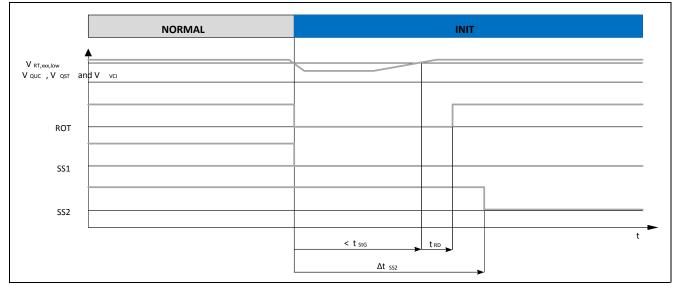

|      |        | 11.4.2.2             | NORMAL -> INIT state due to detected fault           |

|      |        |                      |                                                      |

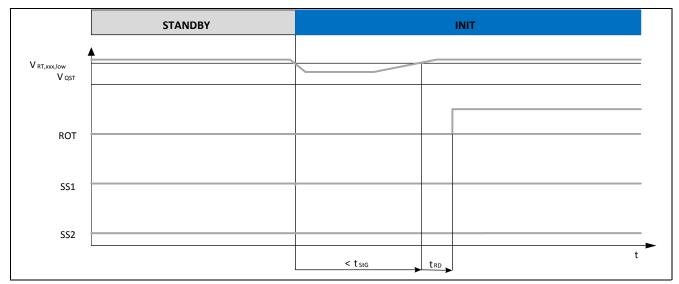

|      |        | 11.4.2.3             | STANDBY -> INIT state due to detected fault          |

|      |        |                      |                                                      |

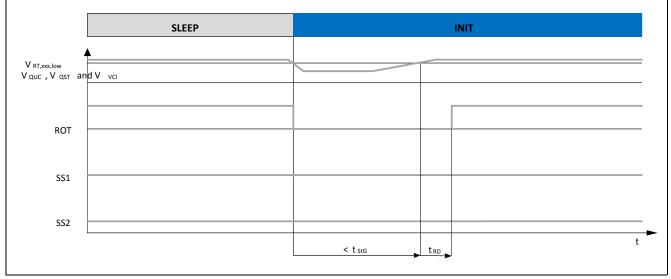

|      |        | 11.4.2.4             | SLEEP -> INIT state due to detected fault            |

|      |        |                      |                                                      |

|      |        | 11.4.2.5             | WAKE -> INIT state due to detected fault             |

|      |        |                      |                                                      |

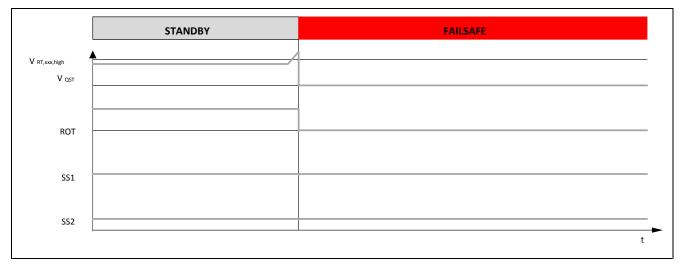

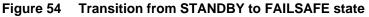

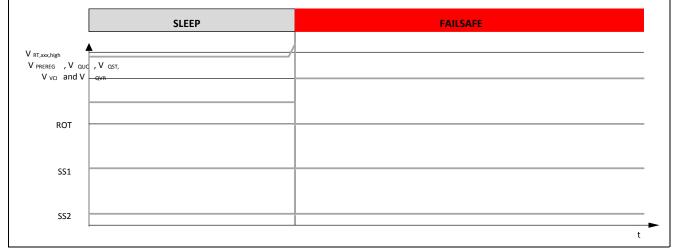

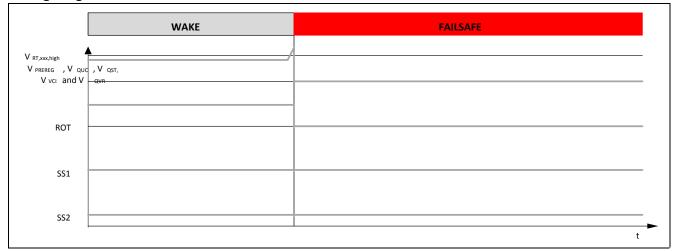

|      | 11.4.3 | Transitio            | n into FAILSAFE State                                |

|      |        |                      | 127                                                  |

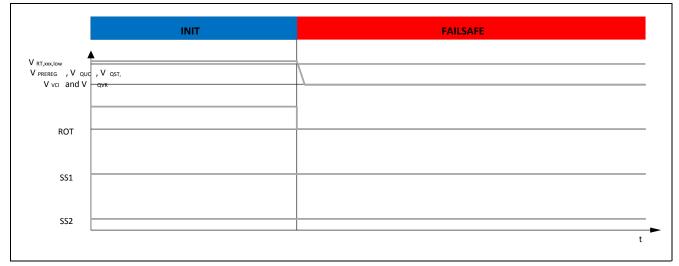

|      |        | 11.4.3.1             | INIT -> FAILSAFE state due to detected fault         |

|      |        |                      |                                                      |

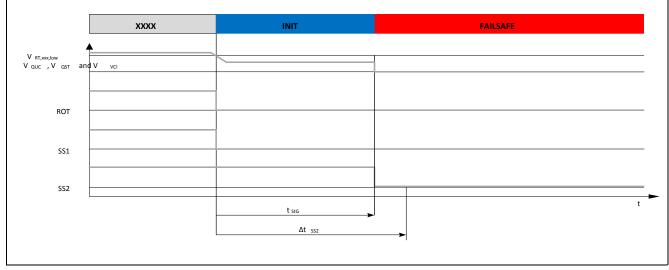

|      |        | 11.4.3.2             | XXXX -> INIT -> FAILSAFE state due to detected fault |

|      |        |                      |                                                      |

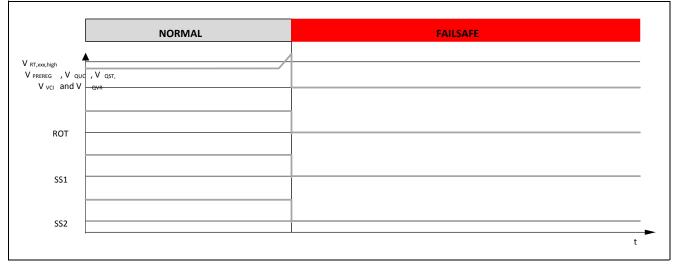

|      |        | 11.4.3.2<br>11.4.3.3 |                                                      |

|      |        |                      |                                                      |

|    |      | 1                                        | 1.4.3.5      | SLEEP -> FAILSAFE state due to Fault                                 |  |  |

|----|------|------------------------------------------|--------------|----------------------------------------------------------------------|--|--|

|    |      | _                                        |              |                                                                      |  |  |

|    |      | 1                                        | 1.4.3.6      | WAKE -> FAILSAFE state due to detected fault                         |  |  |

|    |      |                                          |              |                                                                      |  |  |

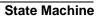

|    |      | 1                                        | 1.4.3.7      | Transition into FAILSAFE state due to thermal shutdown               |  |  |

|    |      |                                          |              | 134                                                                  |  |  |

|    |      | 11.4.4                                   | Transitio    | on into POWERDOWN-state                                              |  |  |

|    |      |                                          |              | 135                                                                  |  |  |

|    | 11.5 | Electric                                 | al Characte  | eristics                                                             |  |  |

|    |      | 136                                      |              |                                                                      |  |  |

|    | 11.6 | Built In<br>138                          | Self Test (I | BIST) Features                                                       |  |  |

|    |      | 11.6.1                                   | Analog I     | Built In Self Test (ABIST)                                           |  |  |

|    |      | 1                                        | 1.6.1.1      | How to run the ABIST                                                 |  |  |

|    |      | -                                        |              |                                                                      |  |  |

|    |      | 1                                        | 1.6.1.2      | Testing the comparator logic only                                    |  |  |

|    |      |                                          | 11.0.1.2     |                                                                      |  |  |

|    |      | 1                                        | 1.6.1.3      | Testing the comparator logic and the corresponding deglitching logic |  |  |

|    |      |                                          | 11.0.1.0     |                                                                      |  |  |

|    |      | 1                                        | 1.6.1.4      | Testing the complete monitoring chain (comparators, deglitching and  |  |  |

|    |      |                                          |              | output)                                                              |  |  |

|    |      | 1                                        | 1.6.1.5      | Abort conditions for ABIST operation                                 |  |  |

|    |      |                                          |              | 145                                                                  |  |  |

|    |      | 11.6.2                                   | Logic Bu     | uilt In Self Test                                                    |  |  |

|    |      |                                          |              | 146 11.7 Microcontroller Programming Support                         |  |  |

|    |      |                                          |              |                                                                      |  |  |

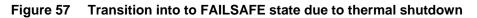

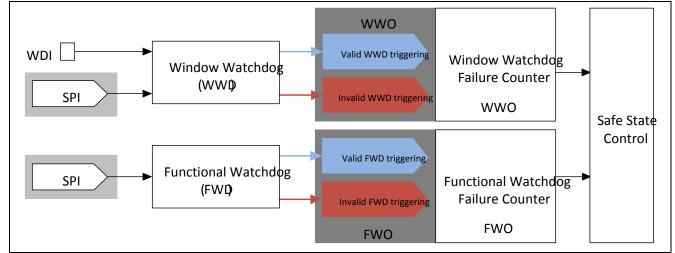

| 12 | Safe | State Con                                | trol Funct   | ion                                                                  |  |  |

| 14 | 12.1 |                                          |              |                                                                      |  |  |

|    | 12.1 | 148                                      |              |                                                                      |  |  |

|    | 12.2 |                                          |              |                                                                      |  |  |

|    |      | 151                                      |              |                                                                      |  |  |

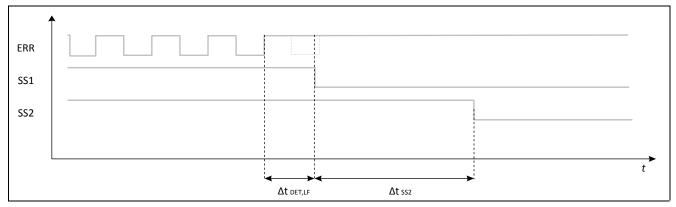

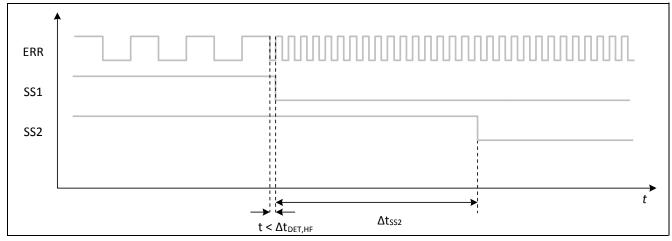

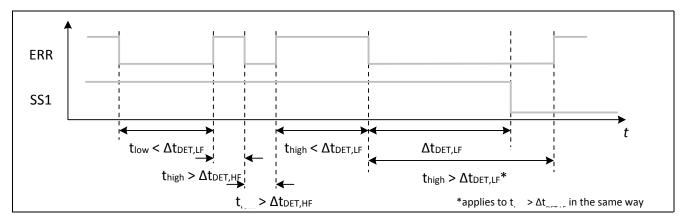

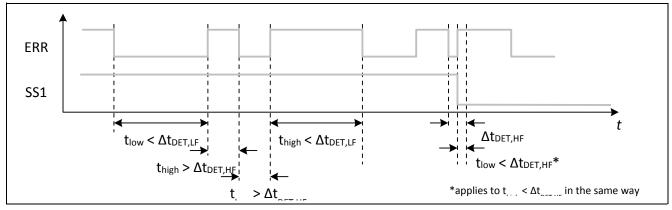

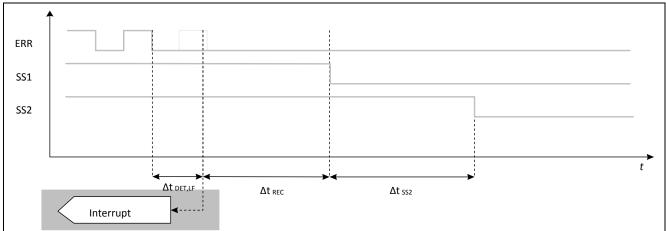

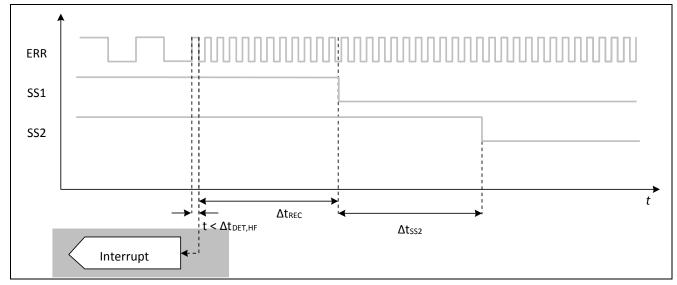

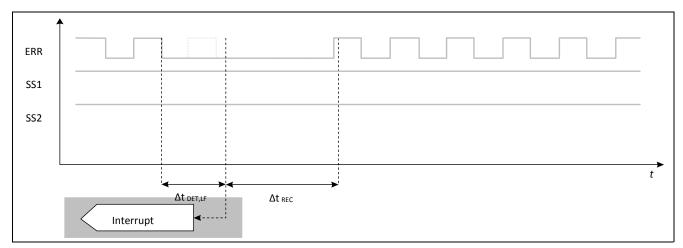

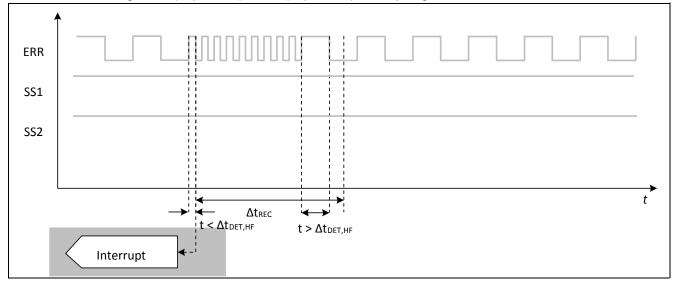

|    | 12.3 | Reactio                                  | on On Micro  | oprocessor Safety Management Unit (SMU - Pin ERR):                   |  |  |

|    |      | 12.3.1                                   | Immedia      | ate reaction on ERR monitoring failure                               |  |  |

|    |      | 12.0.1                                   |              | •                                                                    |  |  |

|    |      | 12.3.2                                   | Recover      | y delay reaction on ERR monitoring failure                           |  |  |

|    |      |                                          |              | · · ·                                                                |  |  |

|    | 12.4 |                                          |              | Triggered State Transitions                                          |  |  |

|    |      | 158                                      |              |                                                                      |  |  |

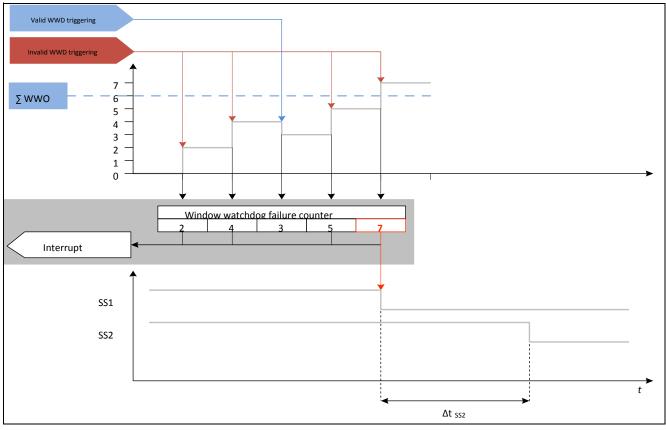

|    | 12.5 | Reaction On Window Watchdog Output (WWO) |              |                                                                      |  |  |

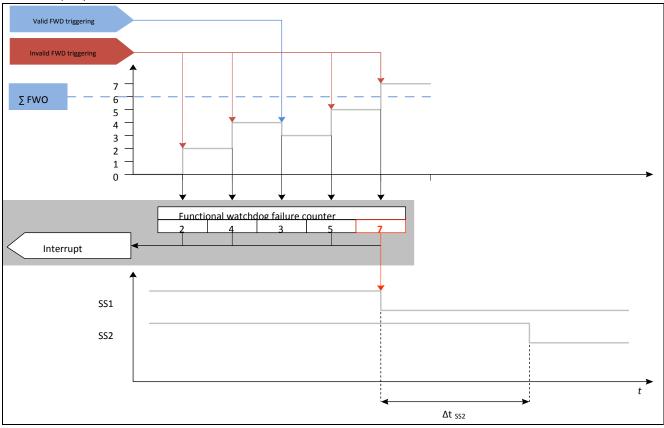

|    | 12.6 | Reactio                                  | n On Func    | tional Watchdog Output (FWO)                                         |  |  |

|    |      |                                          |              | on On Thermal Shutdown (TSD)                                         |  |  |

|    |      |                                          | 161          |                                                                      |  |  |

| 40 |      |                                          |              |                                                                      |  |  |

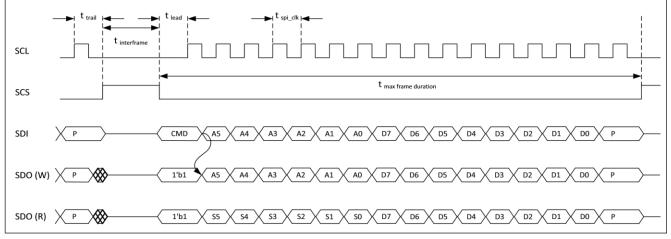

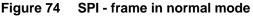

| 13 |      |                                          | -            | terface                                                              |  |  |

|    | 13.1 |                                          |              |                                                                      |  |  |

|    |      | 162                                      |              |                                                                      |  |  |

|    | 13.2 |                                          | te Access    | To Protected Registers                                               |  |  |

|    |      | 165                                      |              |                                                                      |  |  |

|    | 13.3                                      | SPI Wri<br>166 | te Initiated S | State Transition Request And Regulator Configuration                 |  |  |  |  |

|----|-------------------------------------------|----------------|----------------|----------------------------------------------------------------------|--|--|--|--|

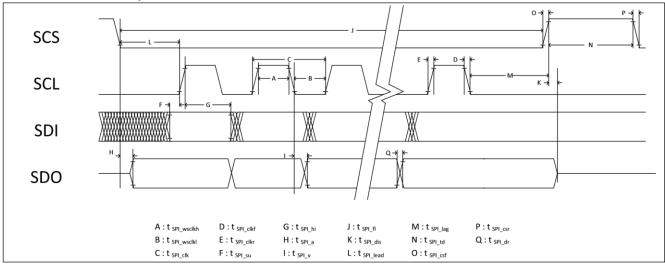

|    | 13.4                                      | Registe        | •              | on                                                                   |  |  |  |  |

|    |                                           | 13.4.1         | Device re      | egisters                                                             |  |  |  |  |

|    |                                           | 13.4.2         | Buck reg       | isters                                                               |  |  |  |  |

|    |                                           |                |                |                                                                      |  |  |  |  |

| 14 | Inter                                     | rupt Gene      | ration         |                                                                      |  |  |  |  |

| 15 | . Window Watchdog And Functional Watchdog |                |                |                                                                      |  |  |  |  |

|    | 15.1                                      |                | -              |                                                                      |  |  |  |  |

|    | 15.2                                      | Window         | v Watchdog     |                                                                      |  |  |  |  |

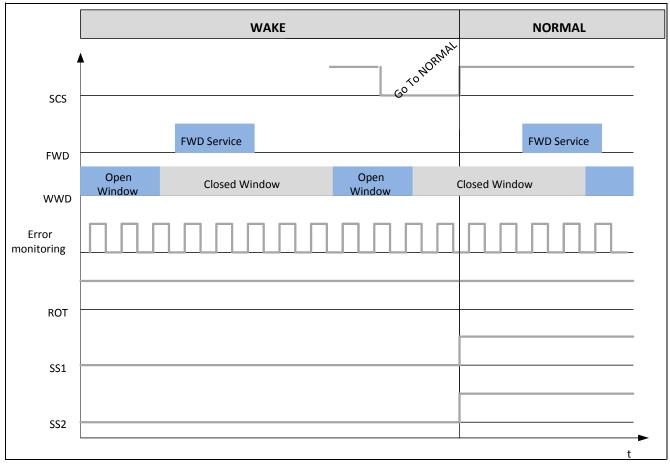

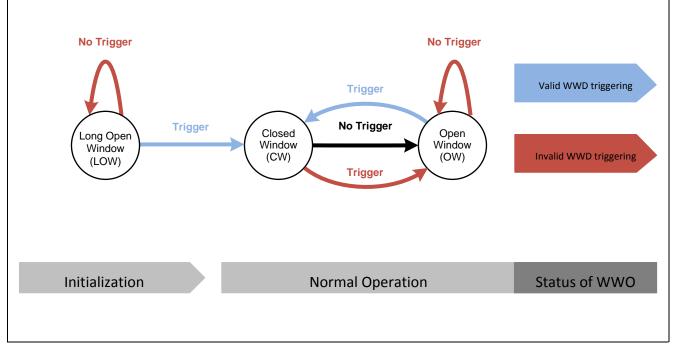

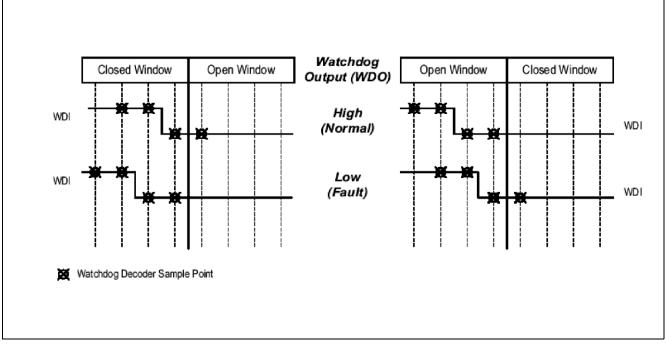

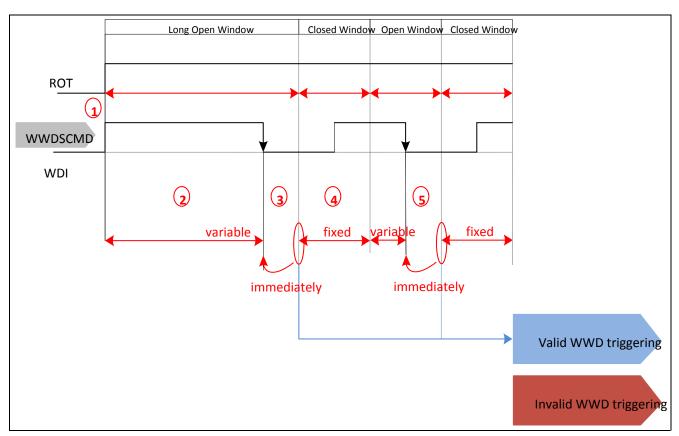

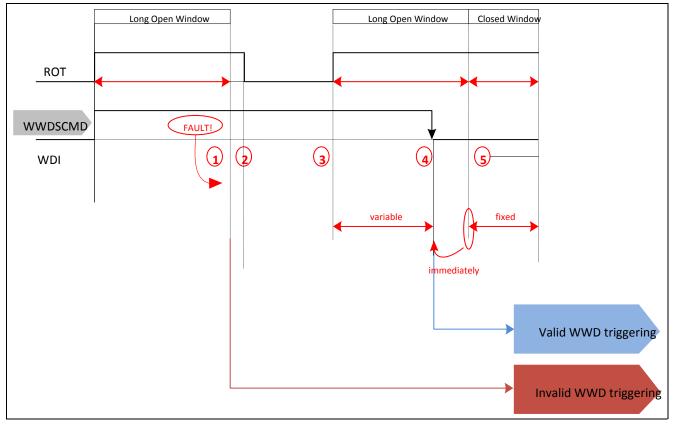

|    |                                           | 15.2.1         | Timing D       | iagrams                                                              |  |  |  |  |

|    |                                           |                |                | . 226                                                                |  |  |  |  |

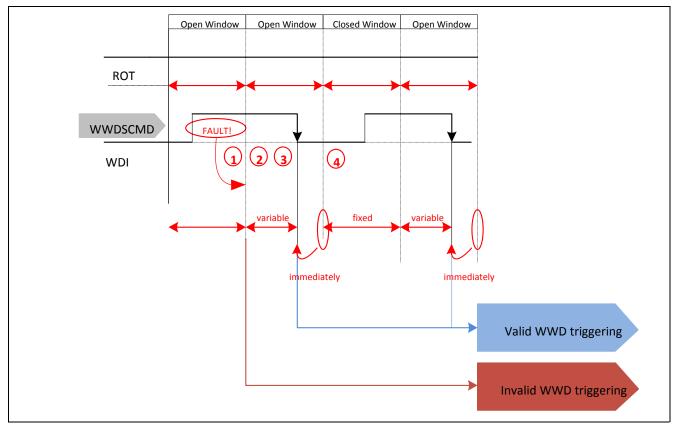

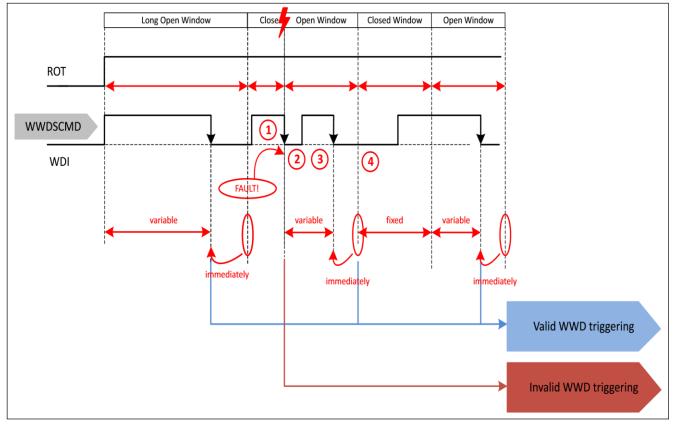

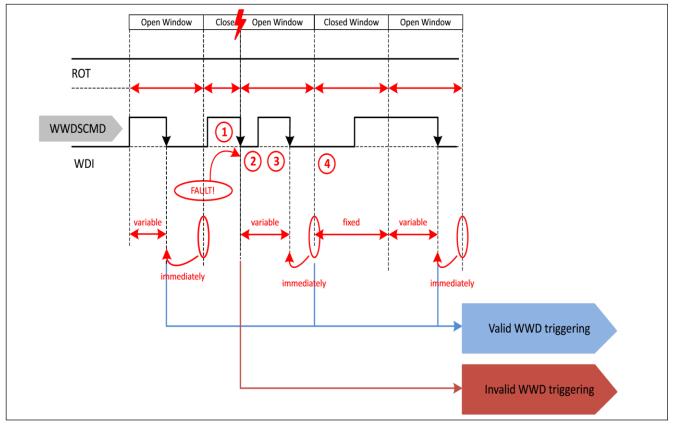

|    |                                           | 1              | 5.2.1.1        | Normal operation: Correct triggering                                 |  |  |  |  |

|    |                                           | 1              | 5.2.1.2        | Fault operation: No trigger in open window after initialization      |  |  |  |  |

|    |                                           |                |                |                                                                      |  |  |  |  |

|    |                                           | 1              | 5.2.1.3        | Fault operation: No trigger in Open Window in steady state           |  |  |  |  |

|    |                                           | 1              | 5.2.1.4        | Fault operation: False trigger in Closed Window after initialization |  |  |  |  |

|    |                                           | 1              | 5.2.1.5        | Fault operation: False trigger in Closed Window in steady state      |  |  |  |  |

|    |                                           | 15.2.2         | Electrical     | characteristics                                                      |  |  |  |  |

|    |                                           | 10.2.2         |                |                                                                      |  |  |  |  |

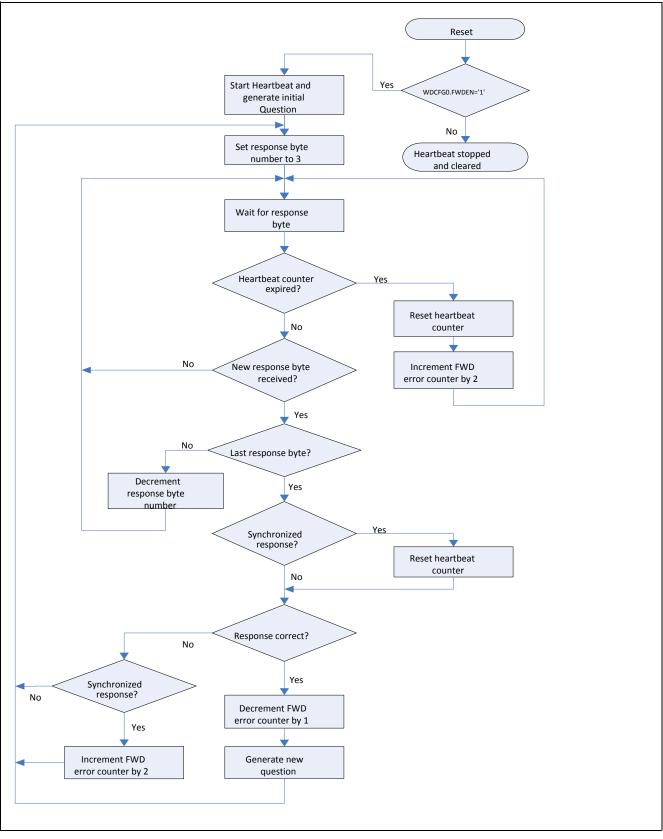

|    | 15.3                                      | Functio        | nal Watchdo    | og                                                                   |  |  |  |  |

|    |                                           | 15.3.1         | Timing D       | iagrams                                                              |  |  |  |  |

|    |                                           |                |                |                                                                      |  |  |  |  |

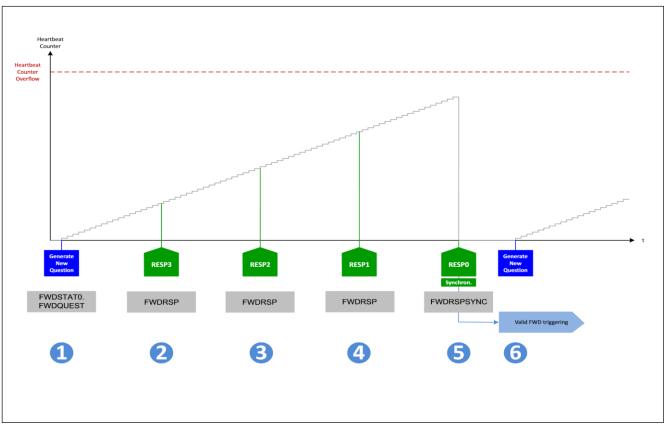

|    |                                           | 1              | 5.3.1.1        | Normal operation: Correct triggering                                 |  |  |  |  |

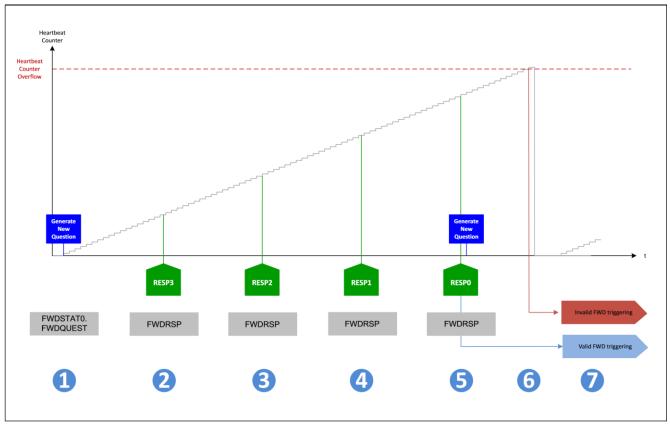

|    |                                           | 1              | 5.3.1.2        | Fault operation: Synchronization is missing                          |  |  |  |  |

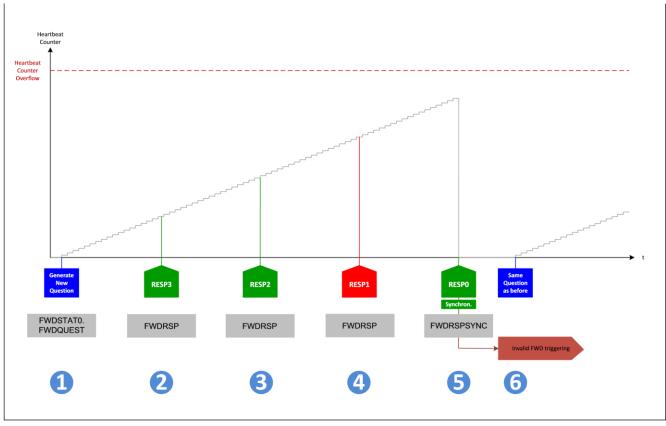

|    |                                           | 1              | 5.3.1.3        | Fault operation: Answer is wrong                                     |  |  |  |  |

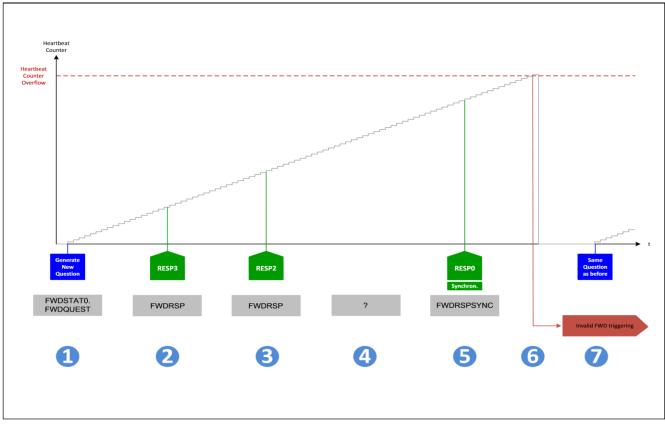

|    |                                           | 1              | 5.3.1.4        | Fault operation: Missing response                                    |  |  |  |  |

|    |                                           |                |                |                                                                      |  |  |  |  |

|    |                                           |                |                |                                                                      |  |  |  |  |

|    |                                           |                |                | Outlines                                                             |  |  |  |  |

|    |                                           |                |                |                                                                      |  |  |  |  |

|    |                                           |                |                |                                                                      |  |  |  |  |

## Multi Voltage Safety Micro Processor Supply

## TLF35584

Overview

#### Features

- · High efficient multi voltage power supply chip

- Serial step up and step down pre regulator for wide input voltage range from 3.0 to 40 V with full performance and low over all power loss

- Low drop post regulator 5.0V/200mA for communication supply (named LDO\_Com)

- Low drop post regulator 5.0 V/600 mA (TLF35584xxVS1) or 3.3 V/600 mA (TLF35584xxVS2) for μC supply (named LDO\_μC)

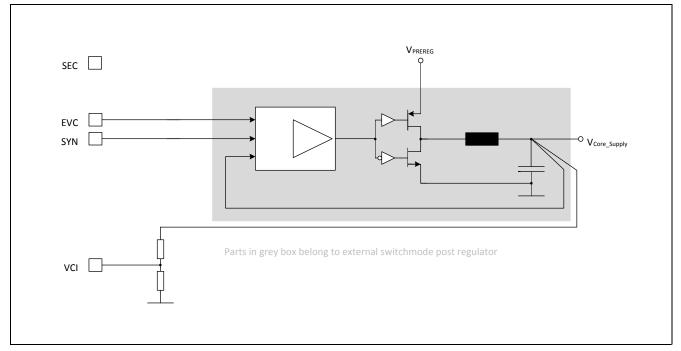

- Provides enable, sync out signal and voltage monitoring (inside device to be added to reset function) for an optional external post regulator for core supply

- Voltage reference 5.0 V +/- 1% for ADC supply, 150 mA current capability (named Volt\_Ref)

- Two trackers for sensor supply following voltage reference 150 mA current capability each (named Tracker 1 and Tracker 2)

- Standby regulator 5.0 V/10 mA (TLF35584xxVS1) or 3.3 V/10 mA (TLF35584xxVS2) (named LDO\_Stby)

- Independent voltage monitoring block with reset function

- · Configurable functional and window watchdog

- 16-bit SPI

- · Safe state control with two safe state signals with programmable delay

- Input voltage monitoring (over voltage switch off)

- Green Product (RoHS compliant)

- ISO26262 compliant

- AEC Qualified

PG-VQFN-48

| Туре                          | Package    | Marking (Line1 / Line2) |

|-------------------------------|------------|-------------------------|

| TLF35584QVVS1 (5.0 V Variant) | PG-VQFN-48 | 35584 / VS1             |

| TLF35584QVVS2 (3.3 V Variant) | PG-VQFN-48 | 35584 / VS2             |

| TLF35584QKVS1 (5.0 V Variant) | PG-LQFP-64 | TLF35584 / QK VS1       |

| TLF35584QKVS2 (3.3 V Variant) | PG-LQFP-64 | TLF35584 / QK VS2       |

#### Pin Configuration Block Diagram

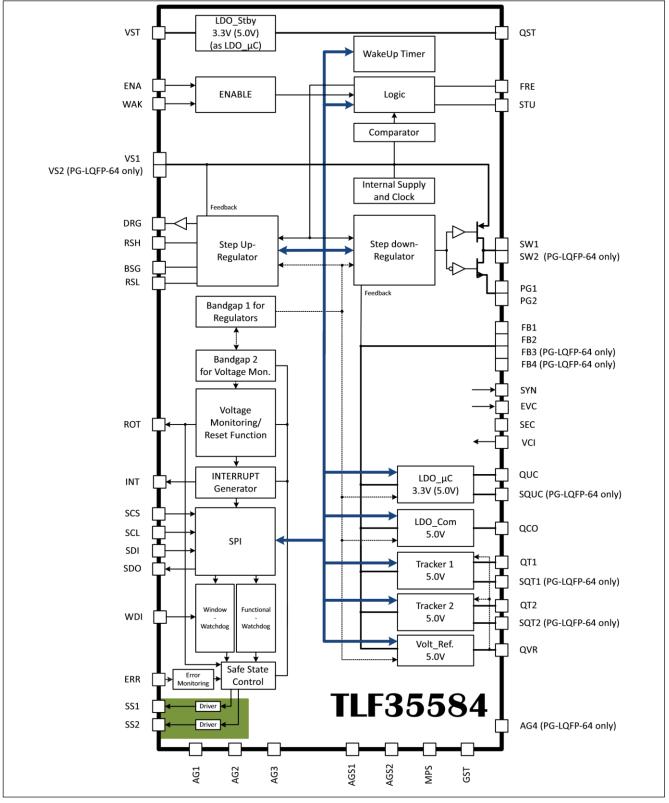

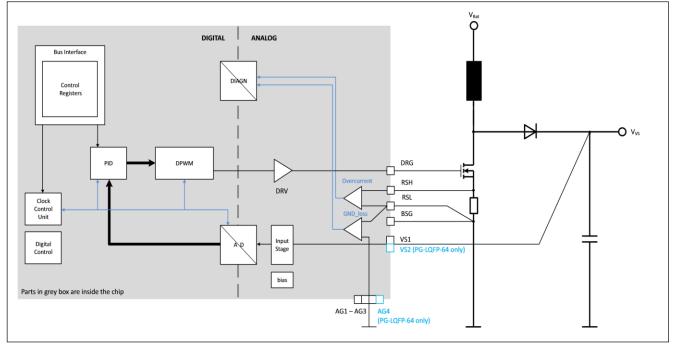

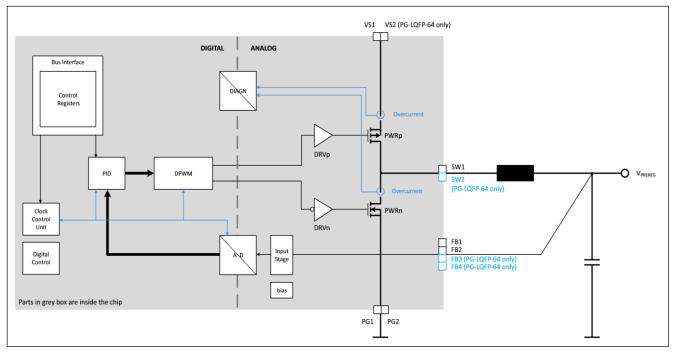

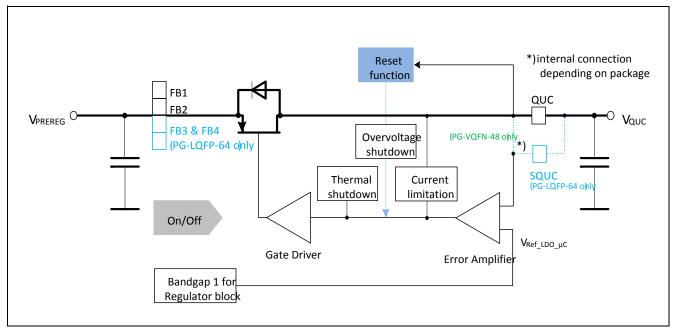

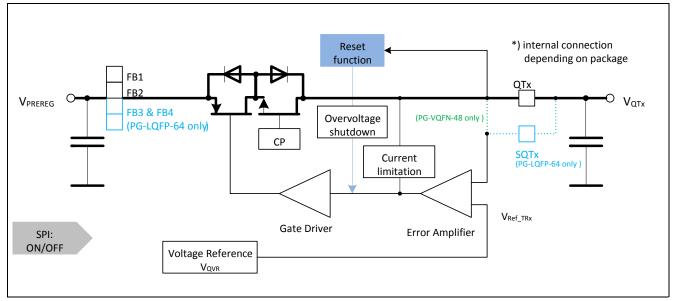

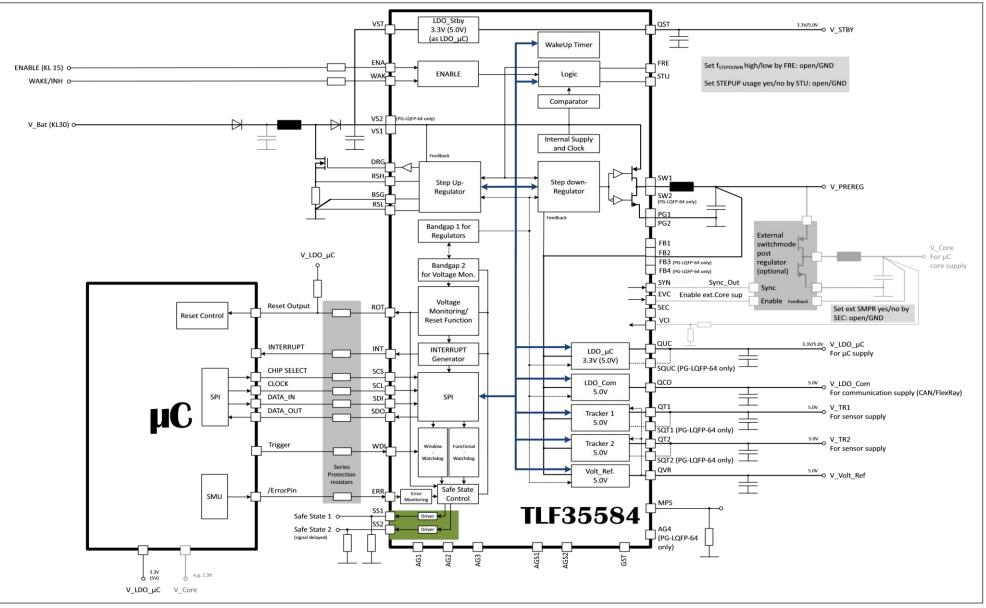

## 2 Block Diagram

Figure 1 Block Diagram

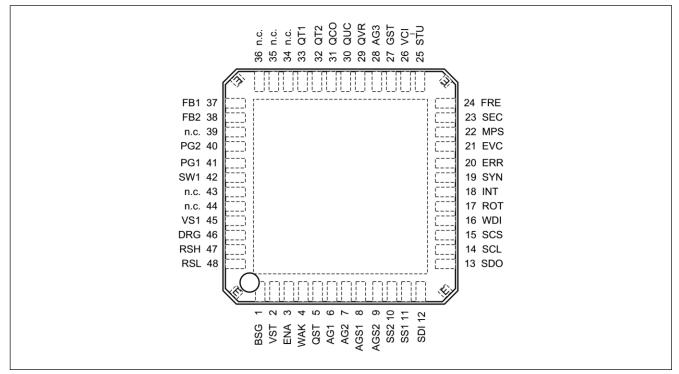

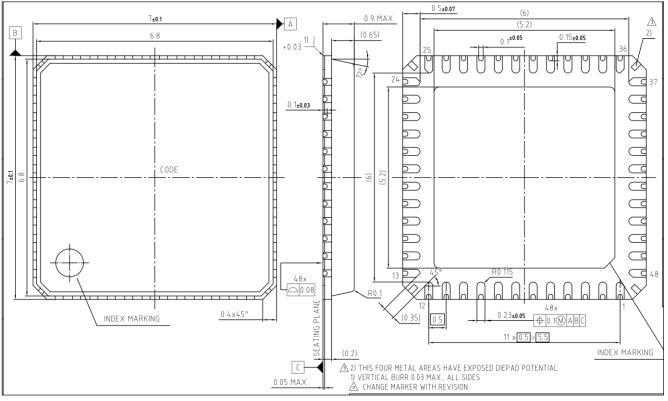

## 3.1 Pin Assignment - PG-VQFN-48

Figure 2 Pin Configuration - PG-VQFN-48

## 3.2 Pin Definitions and Functions - PG-VQFN-48

| Pin | Symbol | Function                                                                                                                                                                                                                                |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BSG    | <b>Boost driver ground:</b><br>Connect this pin to ground at the low side of an external current sense resistor to decouple the driver noise from the sensitive ground. If step up pre regulator option is not used, connect to ground. |

| 2   | VST    | Supply voltage standby regulator, input:<br>Connect this input to supply (battery) voltage with reverse protection diode and<br>capacitor between pin and ground. An EMC filter is recommended.                                         |

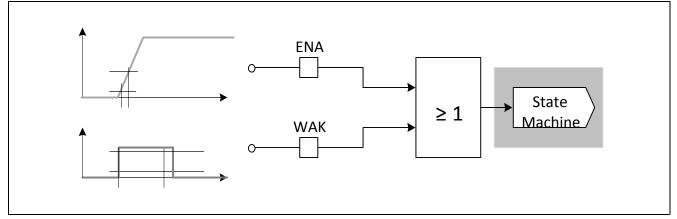

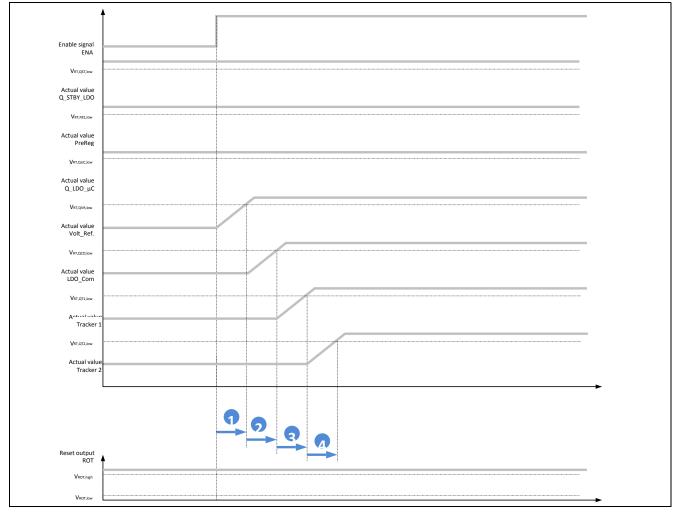

| 3   | ENA    | <b>Enable Input:</b><br>A positive edge signal at this pin will wake the device. In case of not used connect to ground.                                                                                                                 |

| 4   | WAK    | Wake/Inhibit Input:<br>A high level signal of defined length at this pin will wake the device. In case of not<br>used, connect to ground.                                                                                               |

| Pin | Symbol | Function                                                                                                                                                                                                                                            |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | QST    | Output standby LDO:<br>Connect a capacitor as close as possible to pin.                                                                                                                                                                             |

| 6   | AG1    | Analogue ground, pin 1:<br>Connect this pin directly (low ohmic and low inductive) to ground.                                                                                                                                                       |

| 7   | AG2    | Analogue ground, pin 2:<br>Connect this pin directly (low ohmic and low inductive) to ground.                                                                                                                                                       |

| 8   | AGS1   | Analogue ground, safety, pin 1:<br>Connect this pin directly (low ohmic and low inductive) to ground.<br>In case a safety switch is used, connect directly to the source of the NMOS used.                                                          |

| 9   | AGS2   | Analogue ground, safety, pin 2:<br>Connect this pin directly (low ohmic and low inductive) to ground.<br>In case a safety switch is used, connect directly to the source of the NMOS used.                                                          |

| 10  | SS2    | Safe state signal 2:<br>Safe state output signal 2, sets the application into a safe state. Signal is delayed<br>against SS1, delay can be adjusted via SPI command.                                                                                |

| 11  | SS1    | Safe state signal 1:<br>Safe state output signal 1, sets the application into a safe state.                                                                                                                                                         |

| 12  | SDI    | Serial peripheral interface, signal data input:<br>SPI signalling port, connect to SPI port "data output" of micro processor to receive<br>commands during SPI communication.                                                                       |

| 13  | SDO    | Serial peripheral interface, signal data output:<br>SPI signalling port, connect to SPI port "data input" of micro processor to send<br>status information during SPI communication.                                                                |

| 14  | SCL    | Serial peripheral interface, signal clock:<br>SPI signalling port, connect to SPI port "clock" of micro processor to clock the<br>device for SPI communication.                                                                                     |

| 15  | SCS    | Serial peripheral interface, signal chip select:<br>SPI signalling port, connect to SPI port "chip select" of micro processor to address<br>the device for SPI communication.                                                                       |

| 16  | WDI    | Watchdog input, trigger signal:<br>Input for trigger signal, connect the "trigger signal output" of the micro processor<br>to this pin. In case of not used, leave open (internal pull-down).                                                       |

| 17  | ROT    | <b>Reset output:</b><br>Open drain structure with internal pull-up current source. A low signal at this pin indicates a reset event.                                                                                                                |

| 18  | INT    | Interrupt signal:<br>Push-pull-stage. A low pulse at this pin indicates an interrupt, the micro processor<br>shall read out the SPI status registers. Connect to a non maskable interrupt port<br>(NMI) of the micro processor core supply voltage. |

| 19 | SYN | Synchronization output signal:                                                                                                                                                                                                                                                                                          |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |     | Connect this output to the optional external switch mode post regulator synchronization input. The signal delivers the step down regulator switching frequency either in phase or shifted by 180° (selectable via SPI command). The switch mode post regulator shall synchronize to the rising edge. If not used, leave |

|    |     | open.                                                                                                                                                                                                                                                                                                                   |

| Pin | Symbol | Function                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | ERR    | <b>Error signal input:</b><br>Input for error signal from micro processor safety managing unit (SMU, internal failure detection of the micro processor). Connect the "error signal output" of the micro processor to this pin.                                    |

| 21  | EVC    | Enable external post regulator for core supply:<br>Connect this pin to the enable input of the external post regulator. If not used,<br>leave open.                                                                                                               |

| 22  | MPS    | Microcontroller programming support pin:<br>Pull down this pin to ground for operation. Optionally, this pin can be used for<br>microcontroller debugging and programming purposes. For details please refer to<br>Chapter 11.7.                                  |

| 23  | SEC    | <b>Configuration pin for external post regulator for core supply:</b><br>Connect this pin to ground if the option external post regulator is not used. If the option external post regulator is used, leave open.                                                 |

| 24  | FRE    | <b>Frequency adjustment pin:</b><br>Connect pin to ground for low frequency range or leave open for high frequency range.                                                                                                                                         |

| 25  | STU    | <b>Configuration pin for step up converter:</b><br>Connect this pin to ground if the option step up pre regulator is not used. If the option step up pre regulator is used, leave open.                                                                           |

| 26  | VCI    | Input for optional external post regulator output voltage (core supply):<br>Connect an external resistor divider to adjust the over and under voltage<br>thresholds of reset output signal ROT.<br>If the option external post regulator is not used, leave open. |

| 27  | GST    | Gate stress pin:<br>Not for customer use. Connect this pin directly (low ohmic and low inductive) to<br>ground.                                                                                                                                                   |

| 28  | AG3    | Analogue ground, pin 3:<br>Connect this pin directly (low ohmic and low inductive) to ground.                                                                                                                                                                     |

| 29  | QVR    | Output voltage reference:<br>Connect a capacitor as close as possible to pin.                                                                                                                                                                                     |

| 30  | QUC    | Output LDO_uC supply (micro processor supply):<br>Connect a capacitor as close as possible to pin.                                                                                                                                                                |

| 31  | QCO    | Output LDO_communication supply:<br>Connect a capacitor as close as possible to pin.                                                                                                                                                                              |

| 32  | QT2    | Output tracker 2:<br>Connect a capacitor as close as possible to pin.                                                                                                                                                                                             |

| 33 | QT1  | Output tracker 1:<br>Connect a capacitor as close as possible to pin.                                                                                                                                           |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34 | N.C. | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures. |

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                    |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35  | N.C.   | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                             |

| 36  | N.C.   | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                             |

| 37  | FB1    | Step down pre regulator feedback input plus input for linear post regulators<br>and trackers, pin 1:<br>Connect the capacitor of the step down pre regulator output filter with low ohmic<br>and low inductive connection straight to this pin. Always connect in parallel with<br>pin FB2. |

| 38  | FB2    | Step down pre regulator feedback input plus input for linear post regulators<br>and trackers, pin 2:<br>Connect the capacitor of the step down pre regulator output filter with low ohmic<br>and low inductive connection straight to this pin. Always connect in parallel with<br>pin FB1. |

| 39  | N.C.   | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                             |

| 40  | PG2    | <b>Step down pre regulator power ground, pin 2:</b><br>Connect this pin straight (low ohmic and low inductive) to ground and pre regulator output capacitor minus. Always connect in parallel with pin PG1.                                                                                 |

| 41  | PG1    | <b>Step down pre regulator power ground, pin 1:</b><br>Connect this pin straight (low ohmic and low inductive) to ground and pre regulator output capacitor minus. Always connect in parallel with pin PG2.                                                                                 |

| 42  | SW1    | Step down pre regulator power stage output:<br>Connect this pin straight (low ohmic and low inductive) to the pre regulator output filter.                                                                                                                                                  |

| 43  | N.C.   | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                             |

| 44 | N.C. | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                                          |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45 | VS1  | Supply voltage step down pre regulator input:<br>Connect this input to the output of the step up pre regulator. If step up pre regulator<br>option is not used, connect to supply (battery) voltage with reverse protection<br>diode and capacitor between pin and ground. An EMC filter is recommended. |

| Pin             | Symbol | Function                                                                                                                                                                                                                                                                                                 |

|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46              | DRG    | <b>Driver output for external step up regulator power stage, connect to gate:</b><br>Gate of low side switch of step up pre regulator: Connect to the gate of an external N-channel mosfet, line to be straight and as short as possible. If step up pre regulator option is not used, leave open.       |

| 47              | RSH    | Sense resistor for external step up regulator power stage, high side:<br>Connect this pin to the high side of an external current sense resistor to determine<br>the maximum current threshold through the external N-channel mosfet. If step up<br>pre regulator option is not used, connect to ground. |

| 48              | RSL    | Sense resistor for external step up regulator power stage, low side:<br>Connect this pin to the low side of an external current sense resistor to determine<br>the maximum current threshold through the external N-channel mosfet. If step up<br>pre regulator option is not used, connect to ground.   |

|                 | EP1    | <b>Edge pin no 1:</b><br>Keep area below this pin free of ground or other signals, do not solder this pin to ground or any other signal. This pin must be kept free of soldering.                                                                                                                        |

|                 | EP2    | <b>Edge pin no 2:</b><br>Keep area below this pin free of ground or other signals, do not solder this pin to ground or any other signal. This pin must be kept free of soldering.                                                                                                                        |

|                 | EP3    | <b>Edge pin no 3:</b><br>Keep area below this pin free of ground or other signals, do not solder this pin to ground or any other signal. This pin must be kept free of soldering.                                                                                                                        |

|                 | EP4    | <b>Edge pin no 4:</b><br>Keep area below this pin free of ground or other signals, do not solder this pin to ground or any other signal. This pin must be kept free of soldering.                                                                                                                        |

| Coolin<br>g Tab | GND    | Cooling Tab.<br>Connect externally to GND and heat sink area.                                                                                                                                                                                                                                            |

**Pin Configuration**

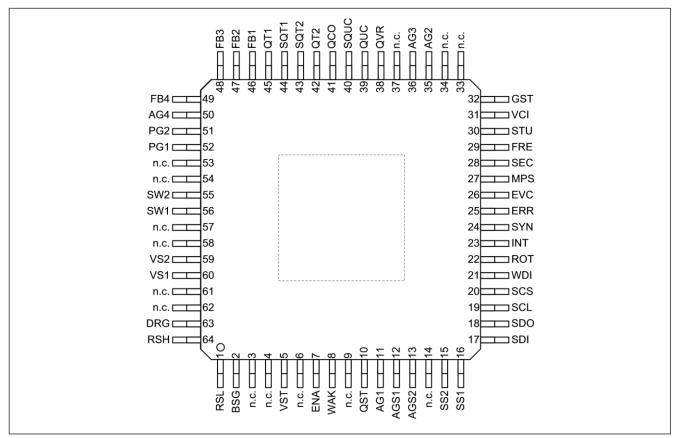

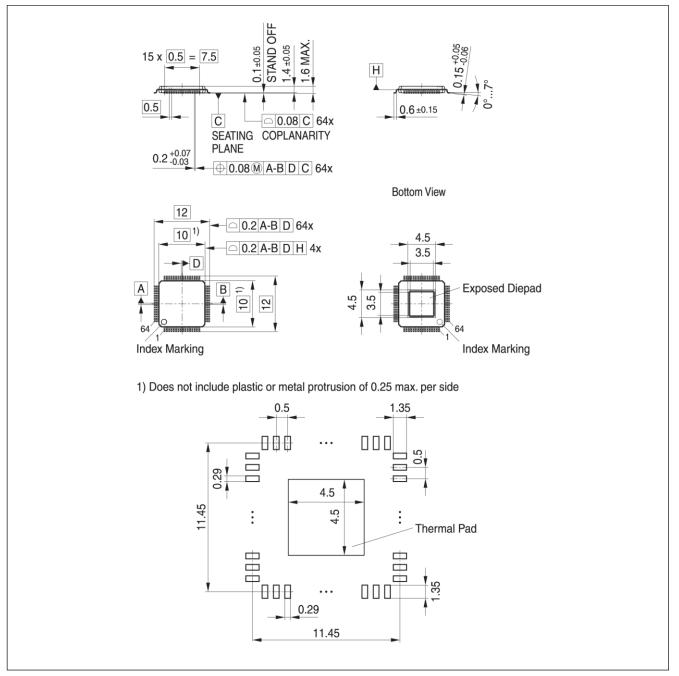

## 3.3 Pin Assignment - PG-LQFP-64

Figure 3 Pin Configuration - PG-LQFP-64

## 3.4 Pin Definitions and Functions - PG-LQFP-64

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                               |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RSL    | Sense resistor for external step up regulator power stage, low side:<br>Connect this pin to the low side of an external current sense resistor to determine<br>the maximum current threshold through the external N-channel mosfet. If step up<br>pre regulator option is not used, connect to ground. |

| 2   | BSG    | <b>Boost driver ground:</b><br>Connect this pin to ground at the low side of an external current sense resistor to decouple the driver noise from the sensitive ground. If step up pre regulator option is not used, connect to ground.                                                                |

| 3   | N.C.   | Internally not connected:<br>This pin is electrically not connected internally and can be kept open/floating,<br>connected to GND or any other signal. Consider neighboring signals for potential<br>failures.                                                                                         |

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                               |

| 4  | N.C. | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures. |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  | VST  | Supply voltage standby regulator, input:<br>Connect this input to supply (battery) voltage with reverse protection diode and<br>capacitor between pin and ground. An EMC filter is recommended.                 |

| 6  | N.C. | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures. |

| 7  | ENA  | <b>Enable Input:</b><br>A positive edge signal at this pin will wake the device. In case of not used, connect to ground.                                                                                        |

| 8  | WAK  | Wake/Inhibit Input:<br>A high level signal of defined length at this pin will wake the device. In case of not<br>used, connect to ground.                                                                       |

| 9  | N.C. | Internally not connected:<br>This pin is electrically not connected internally and can be kept open/floating,<br>connected to GND or any other signal. Consider neighboring signals for potential<br>failures.  |

| 10 | QST  | Output standby LDO:<br>Connect a capacitor as close as possible to pin.                                                                                                                                         |

| 11 | AG1  | Analogue ground, pin 1:<br>Connect this pin directly (low ohmic and low inductive) to ground.                                                                                                                   |

| 12 | AGS1 | Analogue ground, safety, pin 1:<br>Connect this pin directly (low ohmic and low inductive) to ground.<br>In case a safety switch is used, connect directly to the source of the NMOS used.                      |

| 13 | AGS2 | Analogue ground, safety, pin 2:<br>Connect this pin directly (low ohmic and low inductive) to ground.<br>In case a safety switch is used, connect directly to the source of the NMOS used.                      |

| 14 | N.C. | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures. |

| 15 | SS2  | Safe state signal 2:<br>Safe state output signal 2, sets the application into a safe state. Signal is delayed<br>against SS1, delay can be adjusted via SPI command.                                            |

| 16 | SS1  | Safe state signal 1:<br>Safe state output signal 1, sets the application into a safe state.                                                                                                                     |

23

INT

## **Pin Configuration**

| 17  | SDI    | Serial peripheral interface, signal data input:<br>SPI signalling port, connect to SPI port "data output" of micro processor to receive<br>commands during SPI communication.                 |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | SDO    | Serial peripheral interface, signal data output:<br>SPI signalling port, connect to SPI port "data input" of micro processor to send<br>status information during SPI communication.          |

| Pin | Symbol | Function                                                                                                                                                                                      |

| 19  | SCL    | Serial peripheral interface, signal clock:<br>SPI signalling port, connect to SPI port "clock" of micro processor to clock the<br>device for SPI communication.                               |

| 20  | SCS    | Serial peripheral interface, signal chip select:<br>SPI signalling port, connect to SPI port "chip select" of micro processor to address<br>the device for SPI communication.                 |

| 21  | WDI    | Watchdog input, trigger signal:<br>Input for trigger signal, connect the "trigger signal output" of the micro processor<br>to this pin. In case of not used, leave open (internal pull-down). |

| 22  | ROT    | <b>Reset output:</b><br>Open drain structure with internal pull-up current source. A low signal at this pin indicates a reset event.                                                          |

Interrupt signal: Push-pull-stage. A low pulse at this pin indicates an interrupt, the micro processor shall read out the SPI status registers. Connect to a non maskable interrupt port (NMI) of the micro processor core supply voltage.

| 24 | SYN | Synchronization output signal:                                                                                                                                                                                                                                                                                                |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |     | Connect this output to the optional external switch mode post regulator synchronization input. The signal delivers the step down regulator switching frequency either in phase or shifted by 180° (selectable via SPI command). The switch mode post regulator shall synchronize to the rising edge. If not used, leave open. |

| 25 | ERR | <b>Error signal input:</b><br>Input for error signal from micro processor safety managing unit (SMU, internal failure detection of the micro processor). Connect the "error signal output" of the micro processor to this pin.                                                                                                |

| 26 | EVC | Enable external post regulator for core supply:<br>Connect this pin to the enable input of the external post regulator. If not used,<br>leave open.                                                                                                                                                                           |

| 27 | MPS | <b>Microcontroller programming support pin</b> :<br>Pull down this pin to ground for operation. Optionally, this pin can be used for microcontroller debugging and programming purposes. For details please refer to                                                                                                          |

Data Sheet

Chapter 11.7.

| 28 | SEC | <b>Configuration pin for external post regulator for core supply:</b><br>Connect this pin to ground if the option external post regulator is not used. If the option external post regulator is used, leave open.                                                 |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29 | FRE | <b>Frequency adjustment pin:</b><br>Connect pin to ground for low frequency range or leave open for high frequency range.                                                                                                                                         |

| 30 | STU | <b>Configuration pin for step up converter:</b><br>Connect this pin to ground if the option step up pre regulator is not used. If the option step up pre regulator is used, leave open.                                                                           |

| 31 | VCI | Input for optional external post regulator output voltage (core supply):<br>Connect an external resistor divider to adjust the over and under voltage<br>thresholds of reset output signal ROT.<br>If the option external post regulator is not used, leave open. |

| Pin | Symbol | Function                                                                                                                                                                                                        |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32  | GST    | Gate stress pin:<br>Not for customer use. Connect this pin directly (low ohmic and low inductive) to<br>ground.                                                                                                 |

| 33  | N.C.   | Internally not connected:<br>This pin is electrically not connected internally and can be kept open/floating,<br>connected to GND or any other signal. Consider neighboring signals for potential<br>failures.  |

| 34  | N.C.   | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures. |

| 35  | AG2    | Analogue ground, pin 2:<br>Connect this pin directly (low ohmic and low inductive) to ground.                                                                                                                   |

| 36  | AG3    | Analogue ground, pin 3:<br>Connect this pin directly (low ohmic and low inductive) to ground.                                                                                                                   |

| 37  | N.C.   | Internally not connected:<br>This pin is electrically not connected internally and can be kept open/floating,<br>connected to GND or any other signal. Consider neighboring signals for potential<br>failures.  |

| 38  | QVR    | Output voltage reference:<br>Connect a capacitor as close as possible to pin.                                                                                                                                   |

| 39  | QUC    | Output LDO_uC supply (micro processor supply):<br>Connect a capacitor as close as possible to pin.                                                                                                              |

| 40  | SQUC   | Sense connection for LDO_uC supply (micro processor supply):<br>Connect to QUC/LDO_uC externally.                                                                                                               |

| 41  | QCO    | Output LDO_communication supply:<br>Connect a capacitor as close as possible to pin.                                                                                                                            |

| 42 | QT2  | Output tracker 2:<br>Connect a capacitor as close as possible to pin.                                                                                                                                                                                                                             |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43 | SQT2 | Sense connection tracker 2:<br>Connect to QT2/tracker 2 externally.                                                                                                                                                                                                                               |

| 44 | SQT1 | Sense connection tracker 1:<br>Connect to QT1/tracker 1 externally.                                                                                                                                                                                                                               |

| 45 | QT1  | Output tracker 1:<br>Connect a capacitor as close as possible to pin.                                                                                                                                                                                                                             |

| 46 | FB1  | Step down pre regulator feedback input plus input for linear post regulators<br>and trackers, pin 1:<br>Connect the capacitor of the step down pre regulator output filter with low ohmic<br>and low inductive connection straight to this pin. Always connect in parallel with<br>pin FB1 - FB4. |

| 47 | FB2  | Step down pre regulator feedback input plus input for linear post regulators<br>and trackers, pin 2:<br>Connect the capacitor of the step down pre regulator output filter with low ohmic<br>and low inductive connection straight to this pin. Always connect in parallel with<br>pin FB1 - FB4. |

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48  | FB3    | Step down pre regulator feedback input plus input for linear post regulators<br>and trackers, pin 3:<br>Connect the capacitor of the step down pre regulator output filter with low ohmic<br>and low inductive connection straight to this pin. Always connect in parallel with<br>pin FB1 - FB4. |

| 49  | FB4    | Step down pre regulator feedback input plus input for linear post regulators<br>and trackers, pin 4:<br>Connect the capacitor of the step down pre regulator output filter with low ohmic<br>and low inductive connection straight to this pin. Always connect in parallel with<br>pin FB1 - FB4. |

| 50  | AG4    | Analogue ground, pin 4:<br>Connect this pin directly (low ohmic and low inductive) to ground.                                                                                                                                                                                                     |

| 51  | PG2    | <b>Step down pre regulator power ground, pin 2:</b><br>Connect this pin straight (low ohmic and low inductive) to ground and pre regulator output capacitor minus. Always connect in parallel with pin PG1.                                                                                       |

| 52  | PG1    | <b>Step down pre regulator power ground, pin 1:</b><br>Connect this pin straight (low ohmic and low inductive) to ground and pre regulator<br>output capacitor minus. Always connect in parallel with pin PG2.                                                                                    |

| 53  | N.C.   | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                                   |

| 54 | N.C. | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                                                                                               |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55 | SW2  | <b>Step down pre regulator power stage output, pin 2:</b><br>Connect this pin straight (low ohmic and low inductive) to the pre regulator output filter. Always connect in parallel with pin SW1.                                                                                                                                                             |

| 56 | SW1  | Step down pre regulator power stage output, pin 1:<br>Connect this pin straight (low ohmic and low inductive) to the pre regulator output<br>filter. Always connect in parallel with pin SW2.                                                                                                                                                                 |

| 57 | N.C. | Internally not connected:<br>This pin is electrically not connected internally and can be kept open/floating,<br>connected to GND or any other signal. Consider neighboring signals for potential<br>failures.                                                                                                                                                |

| 58 | N.C. | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                                                                                               |

| 59 | VS2  | Supply voltage step down pre regulator, pin 2, input:<br>Connect this input in parallel with VS1 to the output of the step up pre regulator.<br>If step up pre regulator option is not used, connect in parallel with VS1 to supply<br>(battery) voltage with reverse protection diode and capacitor between pin and<br>ground. An EMC filter is recommended. |

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60  | VS1    | Supply voltage step down pre regulator, pin 1, input:<br>Connect this input in parallel with VS2 to the output of the step up pre regulator.<br>If step up pre regulator option is not used, connect in parallel with VS2 to supply<br>(battery) voltage with reverse protection diode and capacitor between pin and<br>ground. An EMC filter is recommended. |

| 61  | N.C.   | Internally not connected:<br>This pin is electrically not connected internally and can be kept open/floating,<br>connected to GND or any other signal. Consider neighboring signals for potential<br>failures.                                                                                                                                                |

| 62  | N.C.   | <b>Internally not connected:</b><br>This pin is electrically not connected internally and can be kept open/floating, connected to GND or any other signal. Consider neighboring signals for potential failures.                                                                                                                                               |

| 63  | DRG    | <b>Driver output for external step up regulator power stage, connect to gate:</b><br>Gate of low side switch of step up pre regulator: Connect to the gate of an external N-channel mosfet, line to be straight and as short as possible. If step up pre regulator option is not used, leave open.                                                            |

| 64              | RSH | Sense resistor for external step up regulator power stage, high side:<br>Connect this pin to the high side of an external current sense resistor to determine<br>the maximum current threshold through the external N-channel mosfet. If step up<br>pre regulator option is not used, connect to ground. |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Coolin<br>g Tab | GND | Cooling Tab.<br>Connect externally to GND and heat sink area.                                                                                                                                                                                                                                            |

## 4.1 Absolute Maximum Ratings

### Table 1 Absolute Maximum Ratings<sup>1)</sup>

$T_j$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                 | Symbol           |      | Value | 5    | Unit | Note /                              | Number   |

|-------------------------------------------|------------------|------|-------|------|------|-------------------------------------|----------|

|                                           |                  | Min. | Тур.  | Max. |      | Test Condition                      |          |

| Voltages                                  |                  |      |       |      |      |                                     |          |

| Boost driver ground                       | VBSG             | -0.3 | -     | 0.3  | V    | -                                   | P_4.1.1  |

| Input standby LDO                         | Vvst             | -0.3 | -     | 40   | V    | 2) 3)                               | P_4.1.2  |

| Input voltage pin 1 (pre regulator)       | V <sub>VS1</sub> | -0.3 | -     | 40   | V    | 2) 3)                               | P_4.1.3  |

| Input voltage pin 2 (pre regulator)       | V <sub>VS2</sub> | -0.3 | -     | 40   | V    | <sup>2) 3)</sup><br>PG-LQFP-64 only | P_4.1.4  |

| External step up power stage, gate        | Vdrg             | -0.3 | -     | 40   | V    | 2) 3)                               | P_4.1.5  |

| External power stage, sense resistor high | VRSH             | -0.3 | -     | 40   | V    | 2) 3)                               | P_4.1.6  |

| External power stage, sense resistor low  | Vrsl             | -0.3 | -     | 6.0  | V    | -                                   | P_4.1.7  |

| Enable                                    | Vena             | -0.3 | -     | 40   | V    | 2) 3)                               | P_4.1.8  |

| Enable                                    | IENA             | -5   | -     | -    | mA   | 4)                                  | P_4.1.9  |

| Wake/Inhibit                              | <i>V</i> wak     | -0.3 | -     | 40   | V    | 2) 3)                               | P_4.1.10 |

| Wake/Inhibit                              | Iwak             | -5   | -     | -    | mA   | 4)                                  | P_4.1.11 |

| Reset output                              | Vrot             | -0.3 | -     | 6.0  | V    | -                                   | P_4.1.12 |

| SPI: Chip select CS                       | Vscs             | -0.3 | -     | 6.0  | V    | -                                   | P_4.1.13 |

| SPI: Clock CLK                            | VSCL             | -0.3 | -     | 6.0  | V    | -                                   | P_4.1.14 |

| SPI: Data_In DI                           | V <sub>SDI</sub> | -0.3 | _     | 6.0  | V    | -                                   | P_4.1.15 |

| SPI: Data_Out DO                          | VSDO             | -0.3 | _     | 6.0  | V    | -                                   | P_4.1.16 |

| Interrupt                                 | VINT             | -0.3 | _     | 6.0  | V    | -                                   | P_4.1.17 |

| Window watchdog trigger                   | Vwdi             | -0.3 | _     | 6.0  | V    | -                                   | P_4.1.18 |

| Error pin                                 | Verr             | -0.3 | _     | 6.0  | V    | _                                   | P_4.1.19 |

| Safe state 1             | V <sub>SS1</sub> | -0.3 | - | 6.0 | V | -               | P_4.1.20 |

|--------------------------|------------------|------|---|-----|---|-----------------|----------|

| Safe state 2             | V <sub>SS2</sub> | -0.3 | - | 6.0 | V | -               | P_4.1.21 |

| Output voltage reference | VQVR             | -0.3 | - | 6.0 | V | -               | P_4.1.22 |

| Output tracker 2         | Vqt2             | -0.3 | - | 40  | V | -               | P_4.1.23 |

| Sense Pin for tracker 2  | Vsqt2            | -0.3 | - | 40  | V | PG-LQFP-64 only | P_4.1.24 |

| Output tracker 1         | Vqt1             | -0.3 | - | 40  | V | -               | P_4.1.25 |

## Table 1 Absolute Maximum Ratings<sup>1)</sup> (cont'd)

$T_j$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                    | Symbol           |      | Value | Values |    | Note /          | Number   |

|------------------------------|------------------|------|-------|--------|----|-----------------|----------|

|                              |                  | Min. | Тур.  | Max.   |    | Test Condition  |          |

| Sense Pin for tracker 1      | VSQT1            | -0.3 | -     | 40     | V  | PG-LQFP-64 only | P_4.1.26 |

| Output LDO_Com               | Vqco             | -0.3 | -     | 6.0    | V  | -               | P_4.1.27 |

| Output LDO_µC                | VQUC             | -0.3 | -     | 6.0    | V  | -               | P_4.1.28 |

| Sense Pin for LDO_µC         | Vsquc            | -0.3 | -     | 6.0    | V  | PG-LQFP-64 only | P_4.1.29 |

| V_Core_Mon ext core supply   | V <sub>VCI</sub> | -0.3 | -     | 6.0    | V  | -               | P_4.1.30 |

| Select ext core supply       | VSEC             | -0.3 | -     | 6.0    | V  | -               | P_4.1.31 |

| Sync_Out ext core supply     | Vsyn             | -0.3 | -     | 6.0    | V  | -               | P_4.1.32 |

| Enable ext core supply       | VEVC             | -0.3 | -     | 6.0    | V  | -               | P_4.1.33 |

| FB_BUCK4                     | $V_{FB4}$        | -0.3 | -     | 7.0    | V  | PG-LQFP-64 only | P_4.1.35 |

| FB_BUCK3                     | V <sub>FB3</sub> | -0.3 | -     | 7.0    | V  | PG-LQFP-64 only | P_4.1.36 |

| FB_BUCK2                     | V <sub>FB2</sub> | -0.3 | -     | 7.0    | V  | -               | P_4.1.37 |

| FB_BUCK1                     | V <sub>FB1</sub> | -0.3 | -     | 7.0    | V  | -               | P_4.1.38 |

| BU_GND2                      | VPG2             | -0.3 | -     | 0.3    | V  | -               | P_4.1.39 |

| BU_GND1                      | VPG1             | -0.3 | -     | 0.3    | V  | -               | P_4.1.40 |

| SW2                          |                  | -0.3 | -     | 40     | V  | PG-LQFP-64 only | P_4.1.41 |

|                              | Vsw2             |      |       |        |    |                 |          |

| SW1                          | Vsw1             | -0.3 | -     | 40     | V  | -               | P_4.1.42 |

| Select step up pre regulator | Vstu             | -0.3 | -     | 6.0    | V  | -               | P_4.1.43 |

| FRE                          | VFRE             | -0.3 | -     | 6.0    | V  | -               | P_4.1.44 |

| Q_STBY                       | VQST             | -0.3 | _     | 6.0    | V  | -               | P_4.1.45 |

| MPS                          | VMPS             | -0.3 | -     | 6.0    | V  | -               | P_4.1.46 |

| Temperatures                 |                  |      |       |        |    |                 | I        |

| Junction Temperature         | Tj               | -40  | -     | 150    | °C | -               | P_4.1.47 |