POWERING INNOVATION

How to Use and Program the New MC33816 High-Performance Fuel Injector Driver Circuit

Ralph C.J. Ferrara

Senior Systems Engineer

FTF-AUT-F0098

Tristan Bosvieux

Automotive Application Engineer

Terry Peterson

Software Engineer

#### June 2012

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, Magnivi, MxC, Platformin a Package, QorlQ Converge, QUICC Engine, Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @ 2012 Freescale Semiconductor, Inc.

### **Agenda**

- Purpose for introducing the MC33816

- Overview of MC33816

- Hardware Circuit functions and features

- Software Instruction set and tools

- MC33816 Applications and Examples

- 3, 4 and 6 cylinder examples

- Peak and Hold waveform generation

- Boost voltage regulator

## Thy is the MC33816 "Smart Injector Driver" Important?

- Many engine manufacturers are turning to Direct Diesel Injection (DDI) and Gasoline Direct Injection (GDI) to increase fuel efficiency and reduce engine emissions, hence the need for a "smart" injector driver.

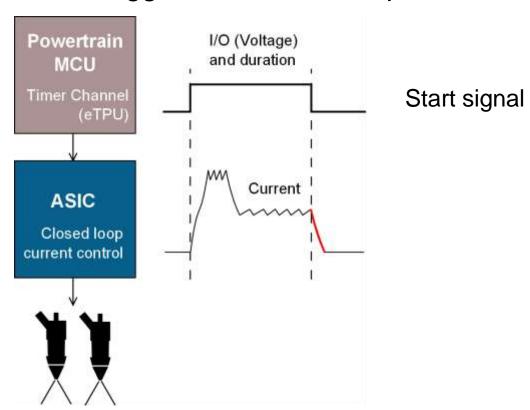

- A "smart" injector driver can off-load tasks from the Engine Control Unit's (ECU's) microcomputer (MCU) by performing the high-speed control algorithms and generating the high voltage necessary to produce the complex peak and hold injector current waveform.

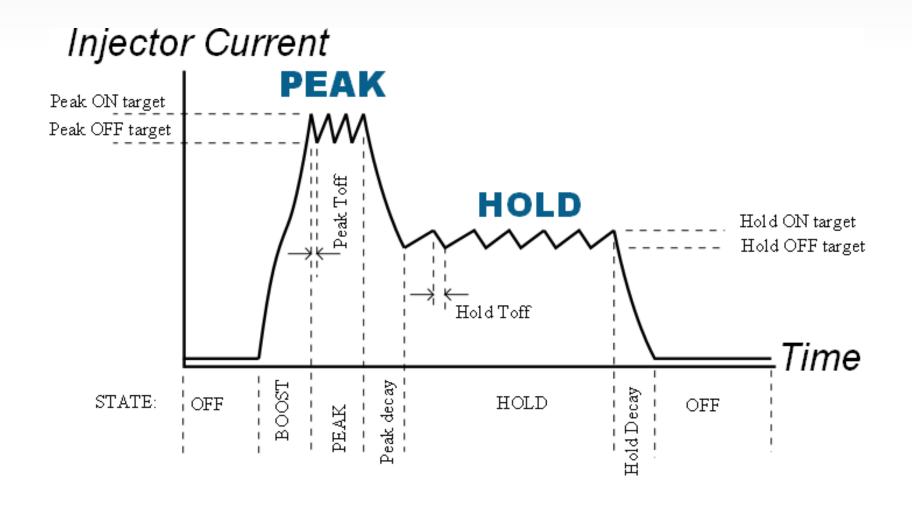

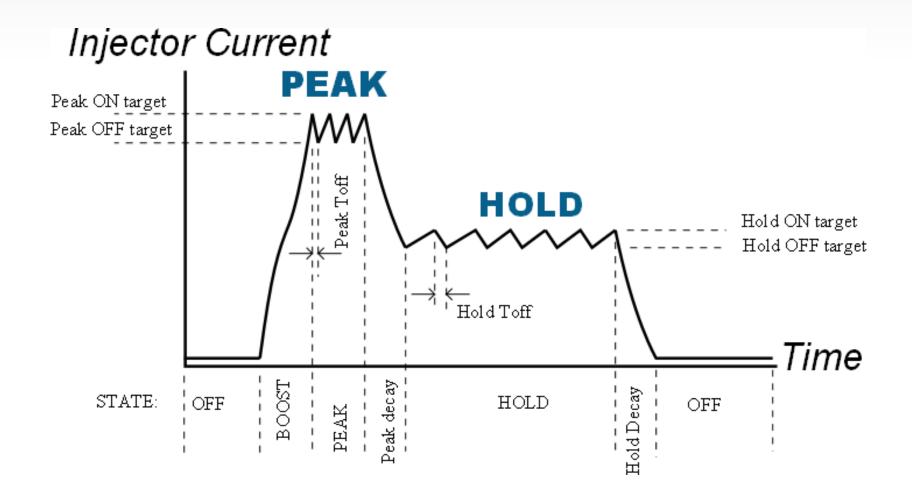

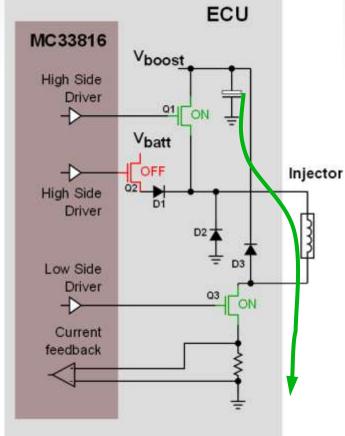

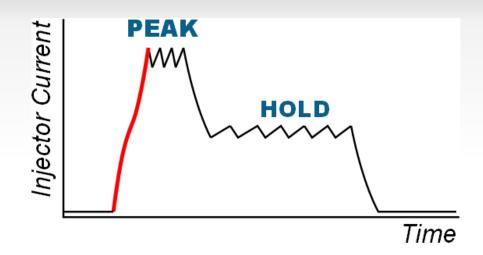

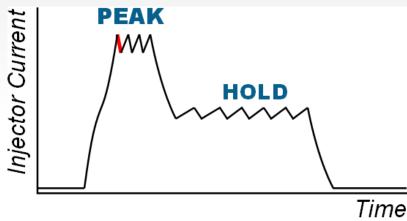

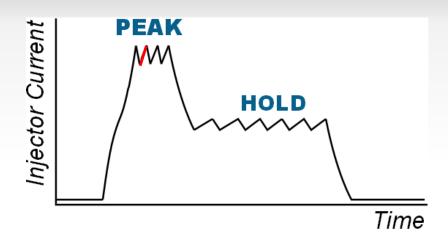

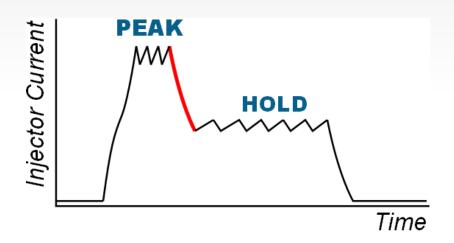

## **Typical Direct Injector Current Waveform**

### **Agenda**

- Purpose for introducing the MC33816

- Overview of MC33816

- Hardware Circuit functions and features

- Software Instruction set and tools

- MC33816 Applications and Examples

- 3, 4 and 6 cylinder examples

- Peak and Hold waveform generation

- Boost voltage regulator

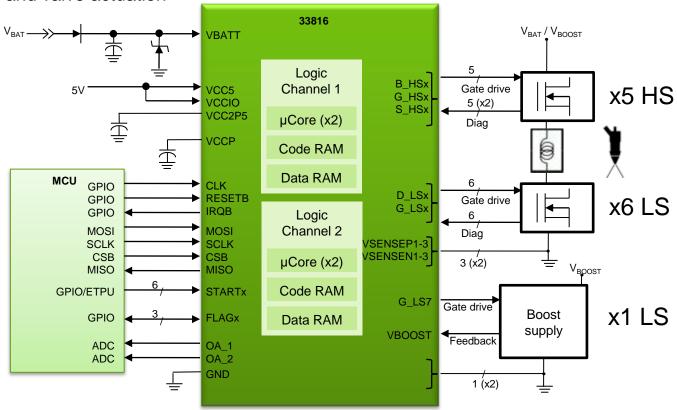

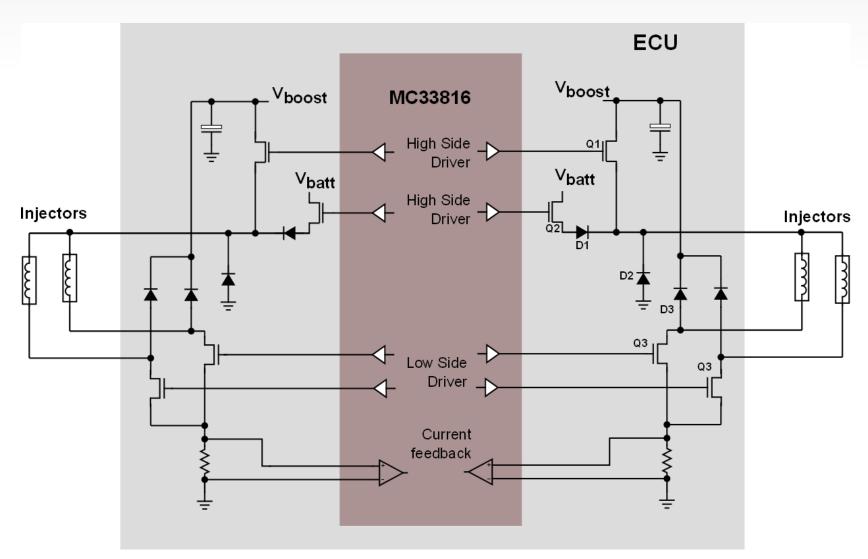

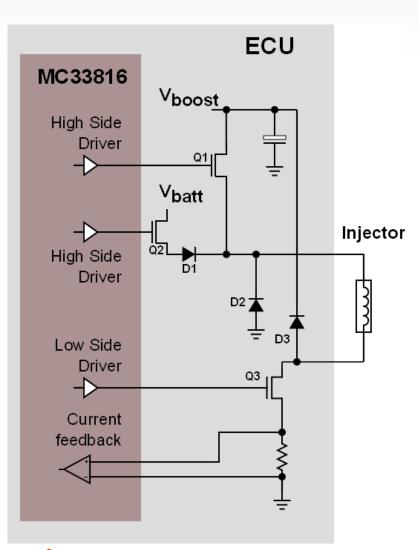

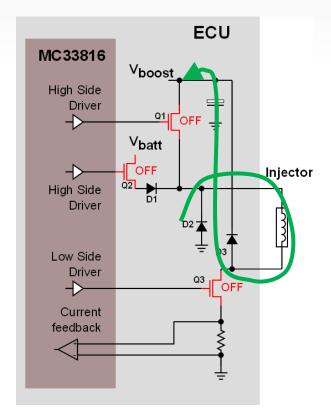

### MC33816 Simplified Application Drawing

- Automotive (12V), Truck and Industrial (24V) Applications Engine Management Systems

- GDI / DDI programmable pre-drivers

- Positioning and dithering of transmission valves

- Solenoid and valve actuation

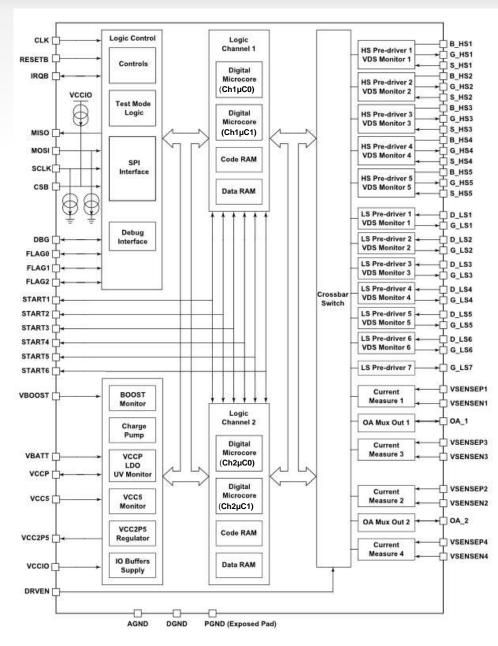

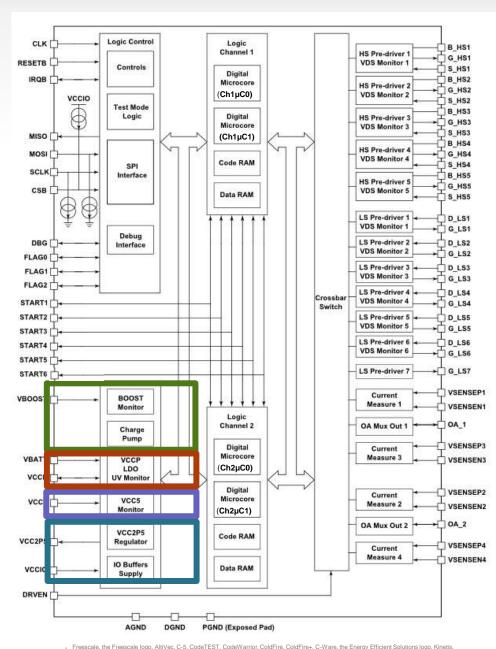

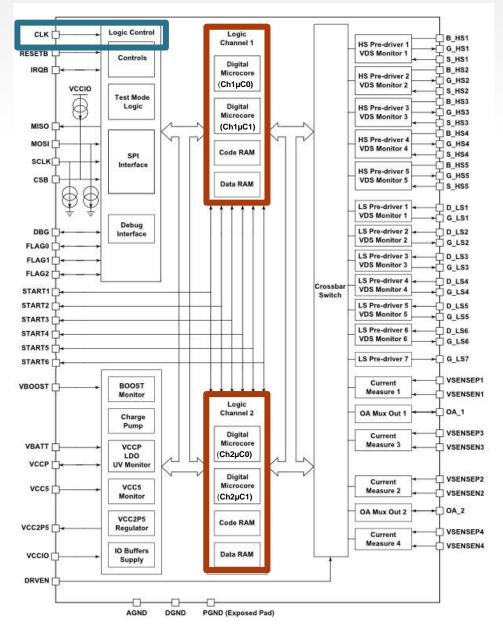

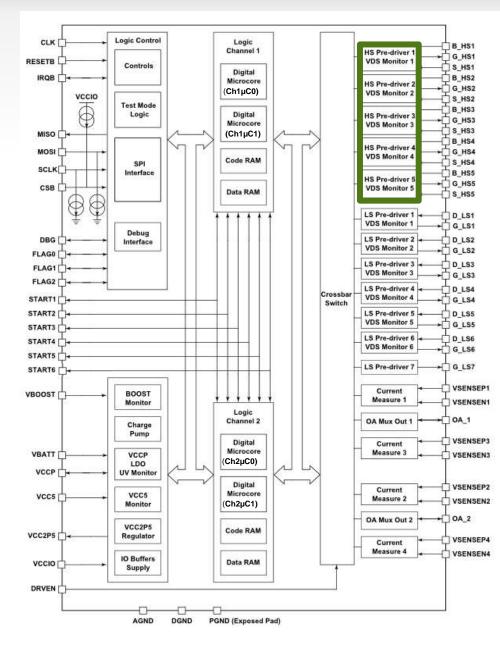

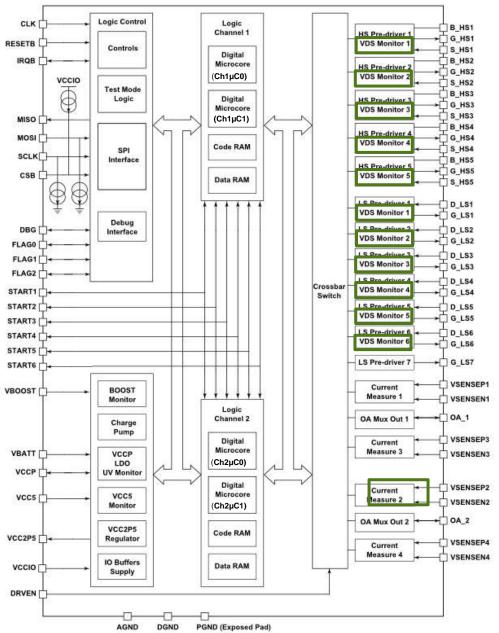

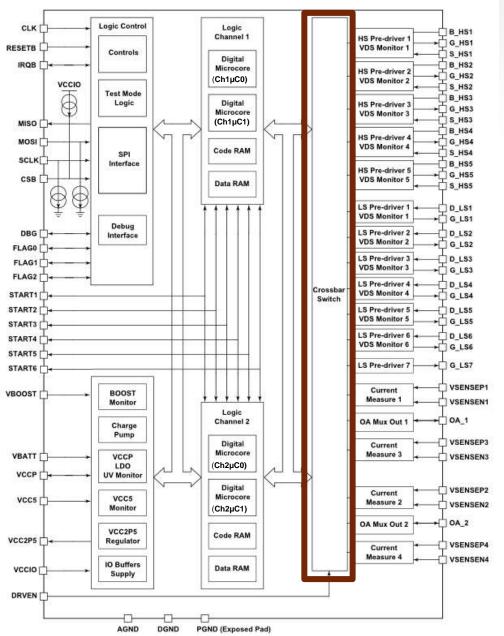

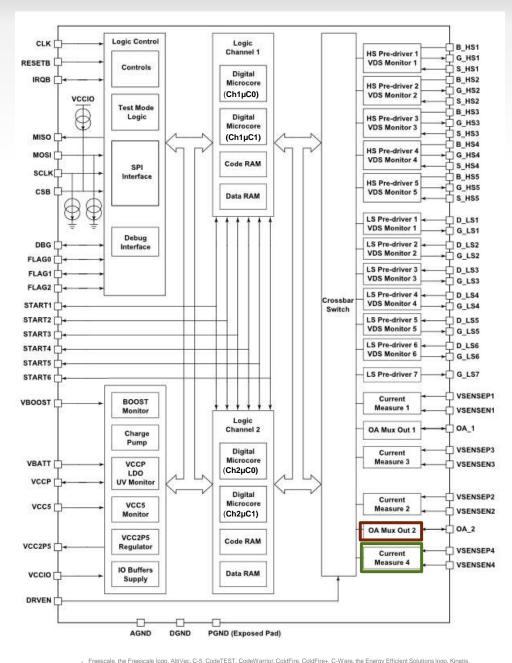

## C33816 Internal Block Diagram

#### Key Features:

- 5 High Side (HS) and 7 Low Side (LS) MOSFET pre-drivers

- 2 Logic Channels, consisting of 2

μCores each, for up to 4

simultaneous threads of code

execution

- Separate Code and Data RAM blocks for each Logic Channel

- 4 current measurement blocks for closed loop current control

- Built-in fault diagnosis and protection

- Power Supply monitoring

- HV DC-DC converter circuitry

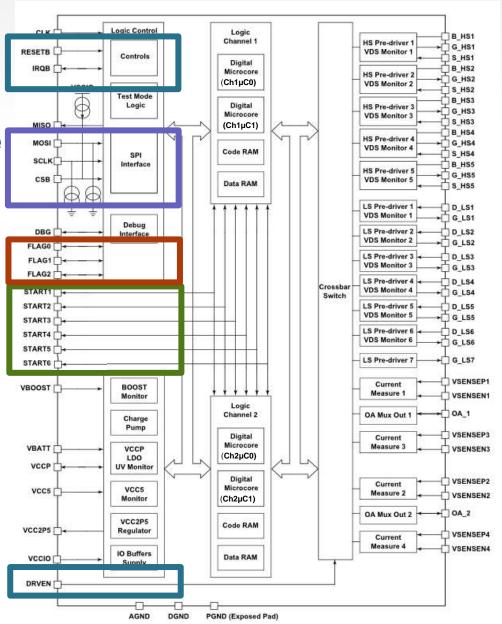

## >mmunication Interfaces

- Communication with MCU via ≤10 mbps SPI interface

- 6 start inputs (STARTx)

- 3 general purpose I/Os (FLAGx)

- Reset and IRQ pins

- Pre-driver enable input (DRVEN)

## wer Supplies and Monitoring

- Boost voltage monitor input with Integrated Charge Pump

- Integrated 7.0V linear regulator (VCCP) for pre-driver power supply (can be externally supplied for 24V battery systems), with under-voltage monitoring

- External VCC5 (5.0V) supply input with under/over-voltage monitoring

- Integrated 2.5V linear regulator for digital core supply, sourced by VCC5 input supply, with under-voltage monitoring

- VCCIO external supply (5.0V or 3.3V) to select reference for digital I/O

- Built-in thermal monitoring for additional protection

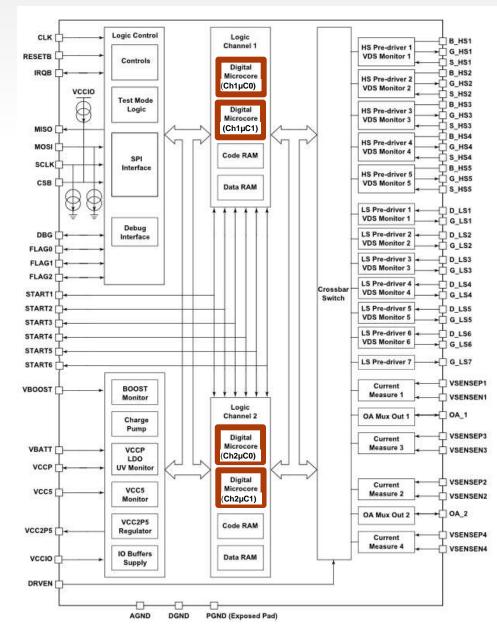

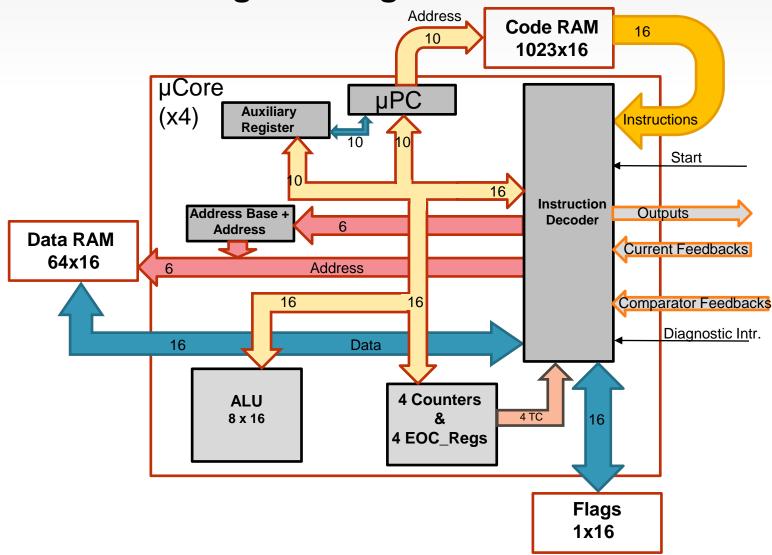

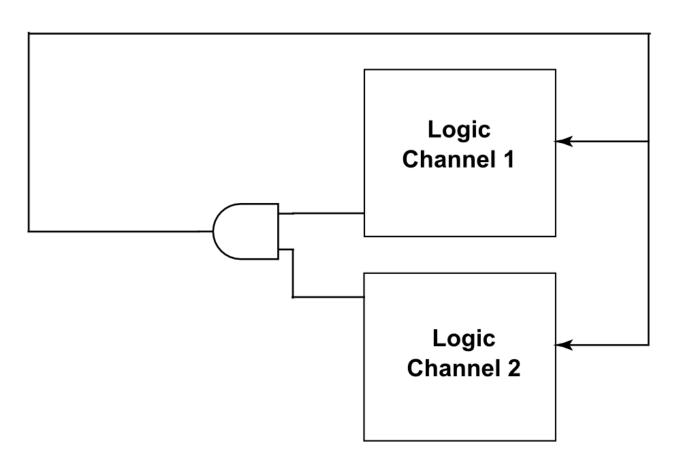

## gic Channels (2x) and PLL Overview

#### 2 Logic Channels

Each logic channel consists of:

- 2 µCores

- Code RAM: 1024 x 16 bits

- Data RAM: 64 x 16 bits

- 2 µCores share 1 Code RAM and 1 Data RAM

- 24 MHz, PLL-generated, system clock sync'd to 1.0 MHz clock

- 1 MHz clock can be provided externally or generated internally.

- Switches automatically to internal clock

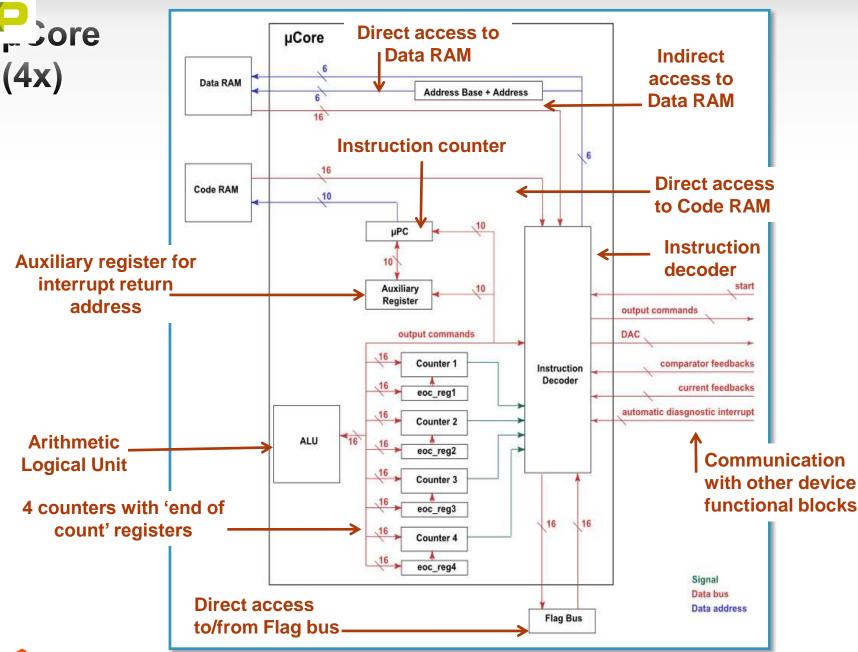

## μCores (4x)

#### Features:

- Single cycle operations:

- Addition

- Subtraction

- Logic operations (not, or, and, xor)

- Shift 8 positions

- Multiple cycle operations:

- Multiplication (32 steps)

- Shift "n" positions ("n" steps)

- 8 General Purpose Registers (16 bits each)

- Arithmetic Condition Register

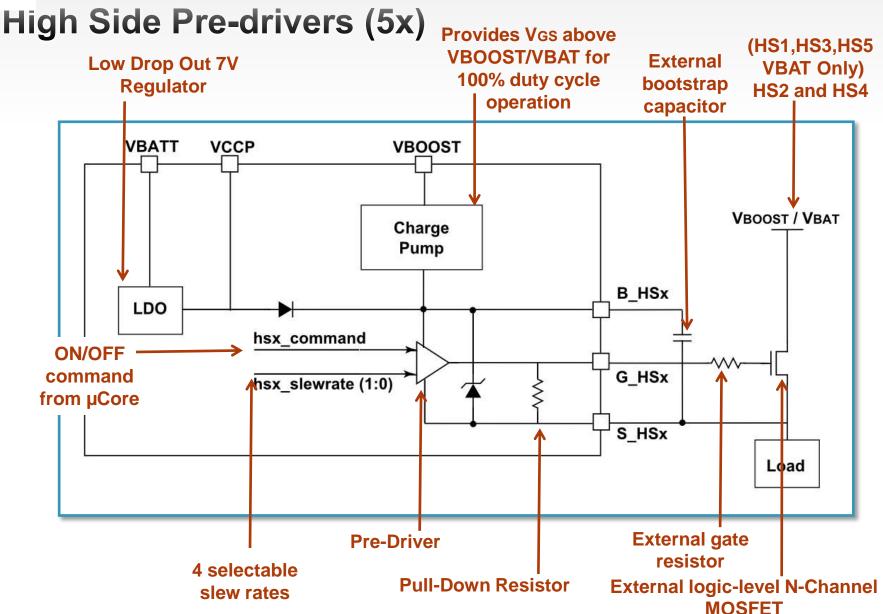

## \_\_gh Side Pre-drivers (5x)

#### 5 high-side pre-drivers

- Require logic-level N-channel MOSFETs

- 4 programmable slew rates

- Vs\_Hsx + 4V < Vb\_Hsx < Vs\_Hsx + 8V</li>

- Vs\_Hsx maximum is 72V

- HS2, HS4 can drive MOSFETs referenced to VBAT or VBOOST

- HS1, HS3, HS5 can only drive MOSFETs referenced to VBAT

- Built-in bootstrap circuitry

- √ Requires external capacitor

- Built-in charge pump with 100% duty cycle capability

- ✓ No external capacitor required

- All high-side drivers can also be used as low-side drivers

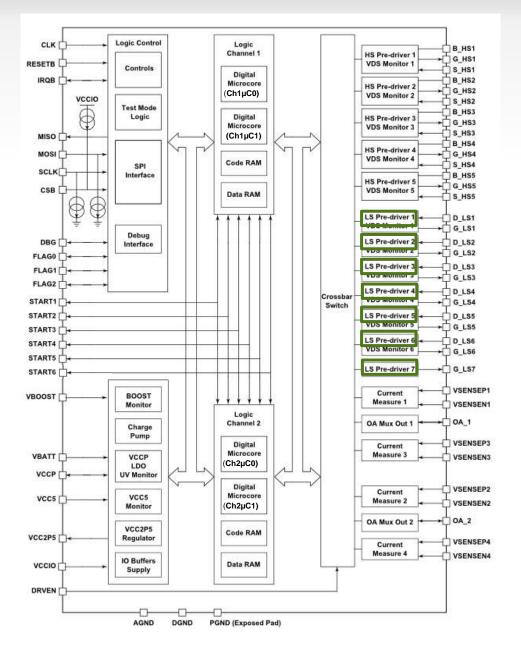

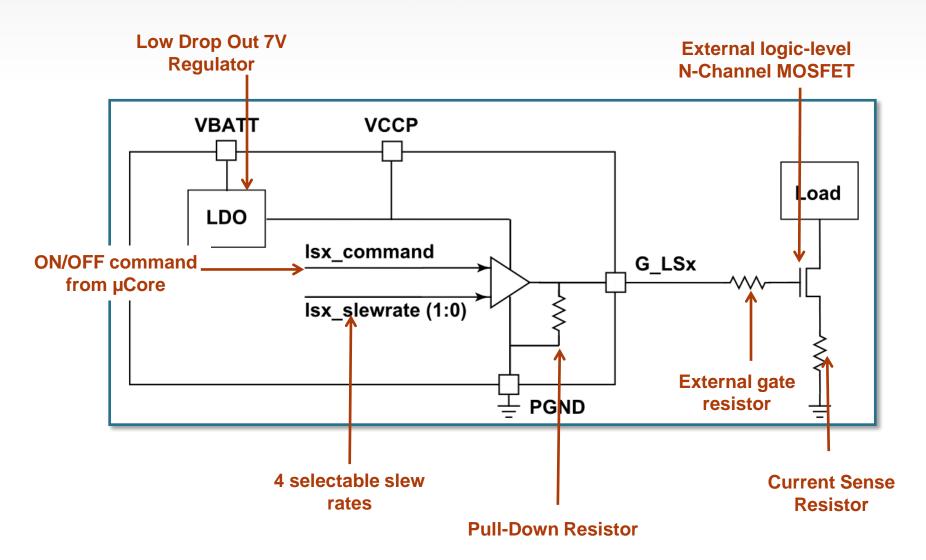

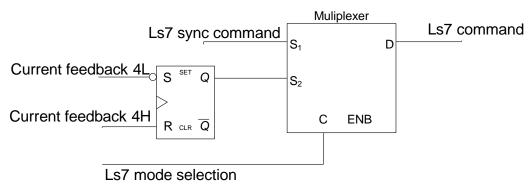

# Side Predrivers (7x)

- 7 low-side pre-drivers for driving logic level N-channel MOSFETs

- 4 programmable slew rates

- LS7 optionally dedicated to DC-DC converter

### Low Side Pre-Drivers (7x)

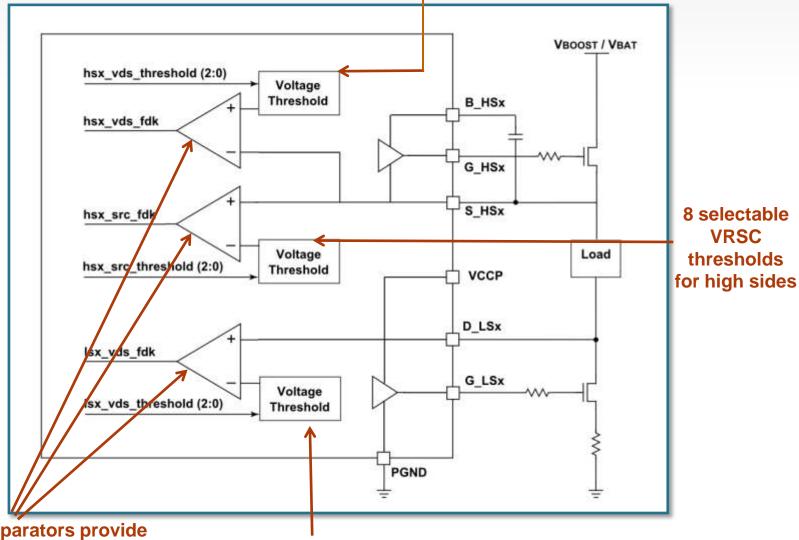

## S and VSRC Monitors

- 5 independent high-side VDS monitors:

- 2 dedicated to VBOOST or VBAT voltage

- 3 dedicated to VBAT voltage only

- 5 independent high-side VSRC monitors

- 6 independent low-side VDS monitors

- Threshold values changed in data registers via microcode or SPI

#### **VDS and VSRC Monitors**

#### , 8 selectable VDS thresholds for high sides

Comparators provide digital fault indications

8 selectable VDS thresholds for low sides

#### **Crossbar Switch**

The Crossbar Switch configures connections between μCores and analog resources

#### Maps μCore control of:

- Outputs

- Slew rate

- Biasing

- VDS Monitors

- Current sense blocks gain

- Current sense blocks feedback gain

- VBOOST DAC setting

- · VBOOST current feedback gain

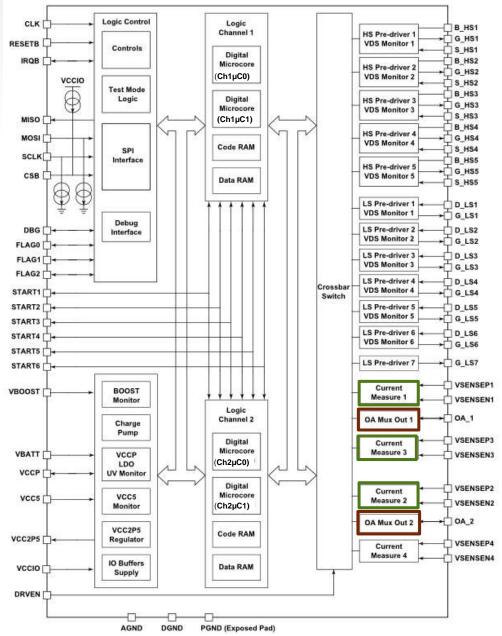

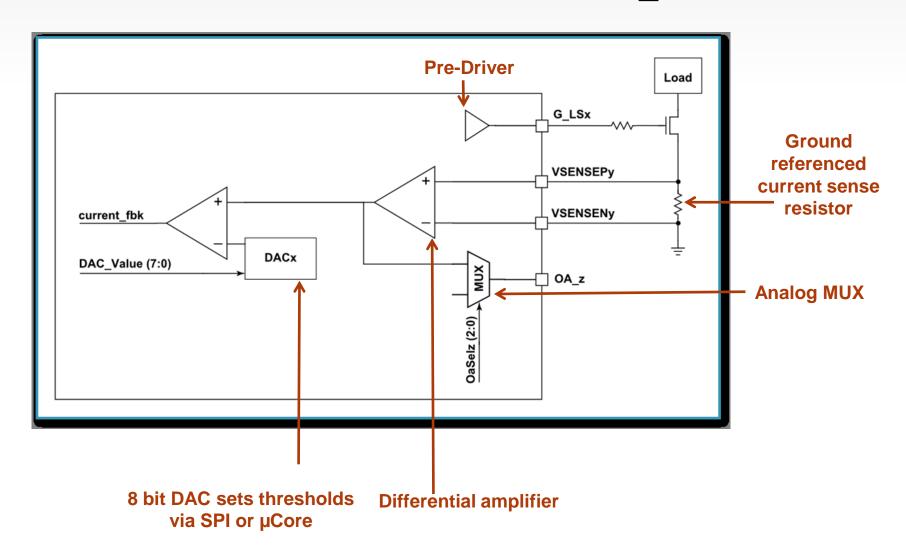

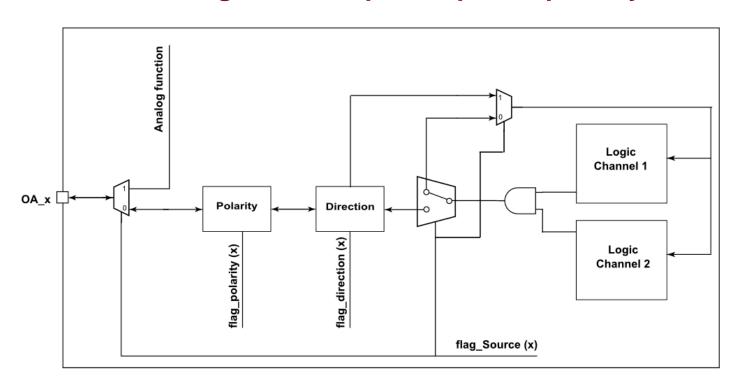

## and OA\_x Blocks

- 3 standard current measurement blocks – single threshold current comparison

- 'Shunt resistor, connected to ground' topology must be used

- 4 values of gain, selected by microcode or SPI

- VSENSE differential voltage can also be routed to OA\_x pin

ADC mode

Automatic offset compensation

### Current Sense Blocks 1,2 & 3 and OA\_x Blocks

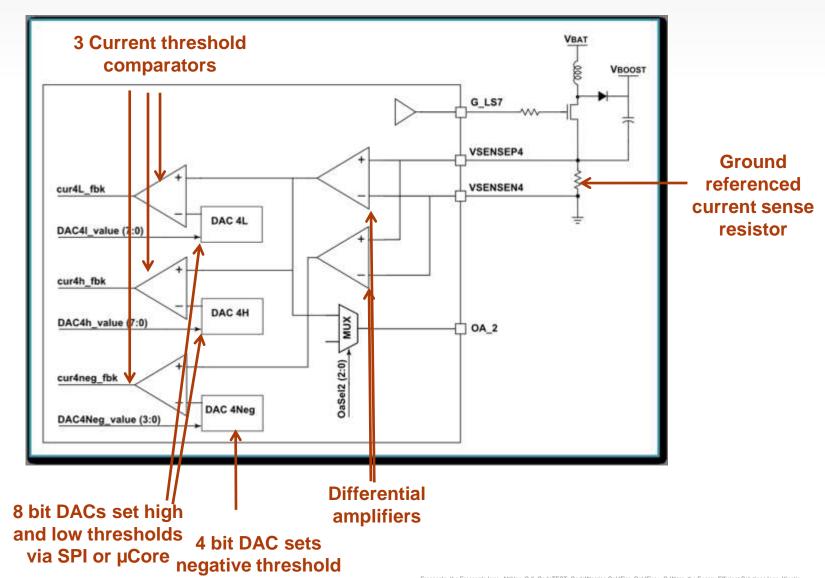

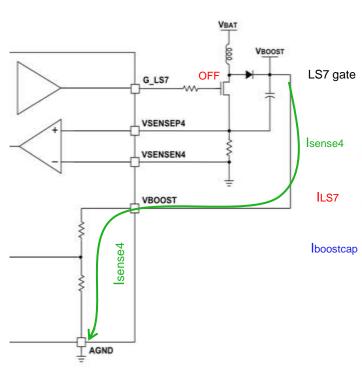

## Jrrent Sense 4 for DC/DC Converter

- 1 specific current measurement block

triple threshold current comparison for DC-DC conversion in current mode

- 'Shunt resistor, connected to ground' topology must be used

- 4 values of gain selected by microcode or SPI

- VSENSE differential voltage can be routed to OA\_2 pin only

#### **Current Sense Block 4 for DC/DC Converter**

via SPI or µCore

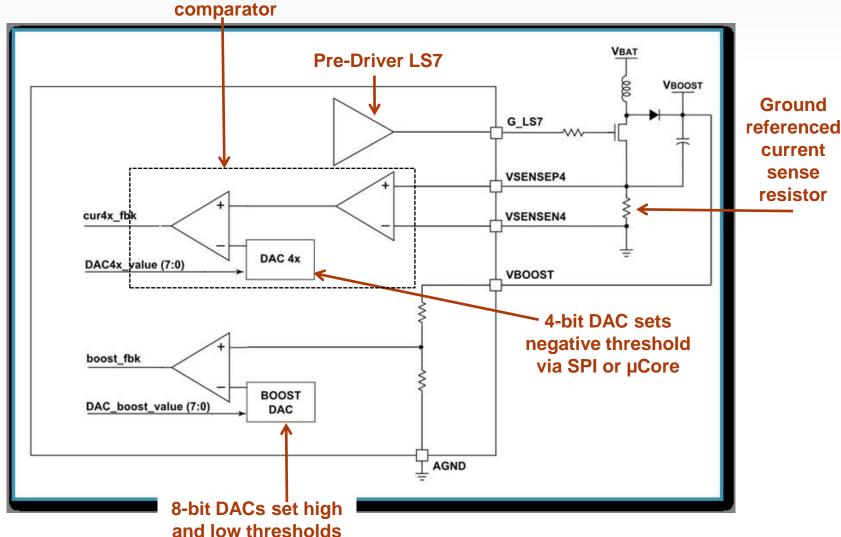

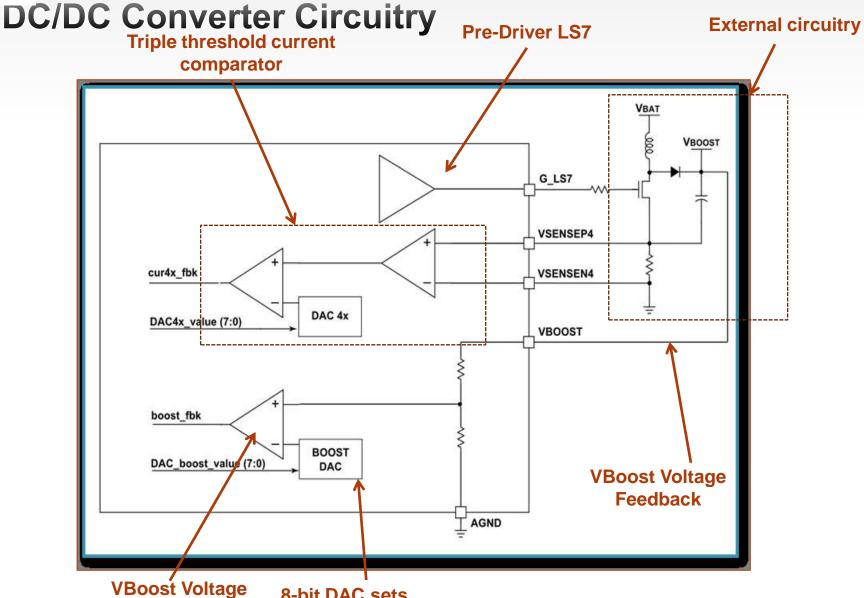

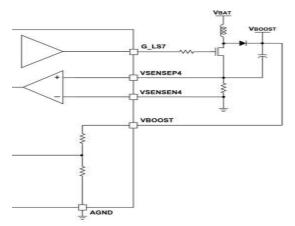

## CDC Converter Circuitry Current measurement block 4 dedicated to BOOST converter

LS7 dedicated to BOOST DC/DC Converter

Boost voltage feedback with integrated divider

**Triple threshold** Regulation loop controlled by means of microcode

Freescale, the Freescale logo, AltiVec. C-5. CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

via SPI or µCore

8-bit DAC sets VBOOST voltage via SPI or µCore

#### Additional MC33816 features

- Ground loss detection

- Loss of connection between one or more ground pins and the system ground will result in a fault indication

- Code RAM memory BIST

- Contents of Code RAM is checked via a Check Sum for bit corruption

- Cipher encryption of Code RAM at download

- Code RAM must be loaded with encrypted code

- Code RAM contents read-out in encrypted form only

- External digital input-output (I/O) able to sustain up to 18V

- Extra safety provided by higher maximum voltage rating on digital I/O pins

- Normal external digital I/O on other products are only able to sustain 7.0 volts

#### MC33816 Internal Flag Bus:

- 16 internal digital flags available

- Certain flags are the bitwise-AND'd from each of the 4 µCores

- Default value is '0'

- Some flags routed to external pins, some are internal

- Used for Inter-processor and Intra-processor communication

- Flag definitions

| Flag number (0-15) | Pin name assigned                  | Defined function type  |

|--------------------|------------------------------------|------------------------|

| 0 to 2             | FLAGx (x=1 to 3)                   | Digital Inputs/Outputs |

| 3 to 8             | STARTx (x=1 to 6)                  | Digital Inputs         |

| 9                  | IRQ (Interrupt Request)            | Digital Output         |

| 10 and 11          | OA_x (x=1, 2)                      | Analog Outputs         |

| 12                 | DBG (Debug)                        | Digital Output         |

| 13 to 15           | No pin assigned (3 Internal flags) |                        |

- STARTx Flags (inputs to the MC33816)

- For MCU to command the MC33816 to begin an injection cycle

- Six STARTx inputs for up to six separate injectors

- FLAGx Flags (Inputs/Outputs to/from the MC33816)

- Can be used by the MC33816 to tell the MCU an injection cycle is completed

- Provide three signals between the MCU and the MC33816

- IRQB Flag (Interrupt Request from the MC33816)

- Initiates MCU interrupt for time critical updates such as fault conditions

- OA Flags (Analog Outputs from Current measurement blocks)

- Provides analog voltage to MCU A/D converter for resolution and accuracy

- Two outputs mux'd to provide outputs from all 4 measurement blocks

- DBG Flag (One debug digital output from MC33816)

- Provides indication of branches taken during program execution

- General Purpose Internal Flags (for inter-core communication)

- Can provide three internal semaphores

### **Agenda**

- Purpose for introducing the MC33816

- Overview of MC33816

- Hardware Circuit functions and features

- Software Instruction set and tools

- MC33816 Applications and Examples

- 3, 4 and 6 cylinder examples

- Peak and Hold waveform generation

- Boost voltage regulator

### **Software – Programming Model**

#### Software – Instruction Set Overview

- 93 instructions in 7 categories:

- Arithmetic Logic Unit (27)

- Configuration (29)

- Diagnostic (3)

- Interrupt and Subroutine (6)

- Jump (16)

- Load (9)

- Wait (3)

## 27 Arithmetic Logic Unit (ALU) Instructions

- 1. add addition of two registers

- 2. addi addition with immediate register

- 3. and mask AND with immediate register

- 4. mul multiplication of two registers

- 5. muli multiplication with immediate value

- 6. not invert contents of a register

- 7. or mask OR with immediate register

- 8. sub subtraction of two registers

- 9. subi subtraction with immediate register

- 10. swap swap high and low bytes of a register

- 11. toc2 performs 2's complement on register

- 12. toint converts 2's complement to integer

- 13. xor mask XOR with immediate register

## 27 ALU Instructions (con't)

- 14. sh32l shift 32-bit register left (register)

- 15. sh32li shift 32-bit register left immediate

- *sh32r* shift 32-bit register right (register)

- 17. sh32ri shift 32-bit register right immediate

- 18. shl shift register left (register)

- 19. shl8 shift register left 8 positions

- 20. shli shift register left immediate

- 21. **shls** shift register left signed (register)

- 22. **shlsi** shift register left signed immediate

- **23. shr** shift register right (register)

- 24. shr8 shift register right 8 positions

- 25. shri shift register right immediate

- **26. shrs** shift register right signed (register)

- 27. shrsi shift register right signed immediate

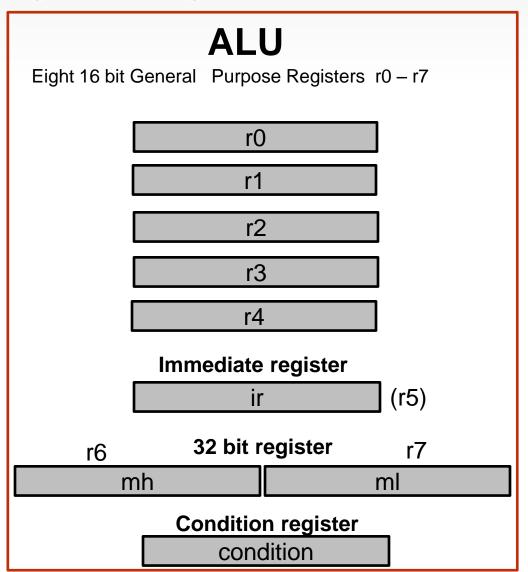

## **ALU – Programming Model**

### **ALU: General Purpose Registers** (r0 – r4)

The ALU general purpose registers (r0 – r4) can be used as:

- Source (operands) for arithmetic and logical operations

- Destination (results) for arithmetic and logical operations

**ALU: 32-bit Register m** (mh = m high & ml = m low) also known as (r6 and r7)

The ALU 32-bit register(mh, ml) can be used as:

- Two general purpose registers (r6 and r7)

- One 32-bit register used for 32-bit shift instructions

- One 32-bit register used in multiplication instructions

## ALU: Immediate Register (ir)

### also known as (r5)

The ALU immediate register (ir) can be used as:

- General purpose register

- SPI address for the SPI backdoor operations

- Offset to modify the address towards the Data Ram.

- Mask value for logic operations (AND, OR, XOR)

- Constant value

## **ALU: Immediate Value (imm)**

The ALU immediate value is a 4-bit (0 – 15) number that can be used as:

- A factor in a multiplication

- An operand in other ALU instructions

# **ALU: 16-bit Condition Register**

| BIT   | NAME           | DESCRIPTION                            |

|-------|----------------|----------------------------------------|

| 15    | SHIFT_OUT      | Shifted out bit                        |

| 14    | CONV_SIGN      | Last conversion sign                   |

| 13    | CARRY          | Carry over bit                         |

| 12-11 | ARITH_LOGIC    | Arithmetic logic                       |

| 10    | MASK_MIN       | Mask result 0x0000                     |

| 9     | MASK_MAX       | Mask result 0xFFFF                     |

| 8     | MUL_SHIFT_OVR  | Multiplication shift overflow          |

| 7     | MUL_SHIFT_LOSS | Multiplication shift precision loss    |

| 6     | RES_ZERO       | Addition or subtraction result is zero |

| 5     | RES_SIGN       | Addition or subtraction sign result    |

| 4     | UNSIGNED_UND   | Unsigned underflow                     |

| 3     | UNSIGNED_OVR   | Unsigned overflow                      |

| 2     | SIGNED_UND     | Signed underflow                       |

| 1     | SIGNED_OVR     | Signed overflow                        |

| 0     | OP_DONE        | Operation complete                     |

#### 29 Configuration Instructions

- 1. bias enables/disables a single bias structure

- 2. **chth** changes threshold on feedback comparator

- 3. **dfcsct** define shortcut for current feedback

- *dfsct* define shortcut for outputs

- 5. rdspi request SPI read

- *c. rstreg* reset register

- 7. **rstsl** reset start latch register

- slab select address base

- slfbk- select feedback source

- 10. slsa selects which register to use as SPI address

- 11. stab load value in address base register

- 12. stadc enables/disables ADC conversion on specified current measurement block

### 29 Configuration Instructions (con't)

- 13. stal set ALU mode

- 14. **stcrb** set control register bit

- 15. stcrt set channel communication register

- 16. **stdcct** set DC/DC control mode

- 17. stdm set DAC register access mode

- 18. **stdrm** set DRAM read mode

- 19. **steoa** enable end of actuation mode

- **20. stf** set flag

- 21. **stfw** set freewheeling mode

- 22. stgn set Op Amp gain

- 23. stirq set interrupt request output pin

- 24. sto set single output

- **25. stoc** set offset compensation

- *26. stos* set output shortcut

## 29 Configuration Instructions (con't)

- 27. stslew set slew rate

- 28. stsrb set status register bit

- 29. wrspi— request SPI write (backdoor)

## 3 Diagnostic Instructions

- endiag enable diagnostics (single)

- endiaga enable diagnostics (all)

- 3. endiags enable diagnostic shortcut

#### 3 Interrupt Instructions

- 1. iconf interrupt configuration

- *iret* return from interrupt

- 3. reqi request for software interrupt

#### 3 Subroutine Instructions

- 1. jtsf jump to subroutine far

- *2. jtsr* jump to subroutine relative

- 3. rfs return from subroutine

#### 16 Jump Instructions

- 1. **jarf j**ump on **a**rithmetic **r**egister **f**ar

- 2. **jarr j**ump on **a**rithmetic **r**egister **r**elative

- 3. jcrf jump on control register far

- 4. **jcrr j**ump on **c**ontrol **r**egister **r**elative

- 5. jfbkf jump on feedback far

- 6. jfbkr jump on feedback relative

- 7. **jmpf** unconditional **jump** far

- 8. **jmpr** unconditional **jump** relative

- 9. **jocf j**ump **o**n flag **c**ondition **f**ar

- 10. jocr jump on flag condition relative

- 11. **joidf j**ump **o**n μcore **id f**ar

- 12. **joidr j**ump **o**n μcore **id r**elative

- 13. joslf jump on start-latch far

## 16 Jump Instructions (con't)

- 14. joslr jump on start-latch relative

- 15. jsrf jump on status register far

- 16. jsrr- jump on status register relative

#### 9 Load Instructions

- cp copy source to destination register

- 2. Idca load counter from register and set outputs

- 3. **Idcd** load counter from DRAM and set outputs

- 4. **Idirh** load immediate register high-byte

- 5. Idirl— load immediate register low-byte

- Idjr1 load jump register 1

- 7. **Idjr2** load jump register 2

- 8. **load** load data from DRAM to register

- store— store data from register to DRAM

#### 3 Wait Instructions

- cwef create wait table entry far

- cwer create wait table entry relative

- 3. wait wait until a condition is verified

- 1. MC33816 Data sheet for hardware reference

- 2. MC33816 Software programming reference manual

- 3. MC33816 EVB with 4 Cylinder and DC/DC software

- 4. Assembler with built-in encryptor

- 5. SPIGen register setting with software download capability

- 6. Software simulator with debug capability\*

- 7. Execution tracing module and software to use the dbg flag pin.\*

\*coming soon

### **Agenda**

- Purpose for introducing the MC33816

- Overview of MC33816

- Hardware Circuit functions and features

- Software Instruction set and tools

- MC33816 Applications and Examples

- 4 cylinder example

- Peak and Hold waveform generation

- Boost voltage regulator

# 4 cylinder configuration, 4 injectors, 2 banks

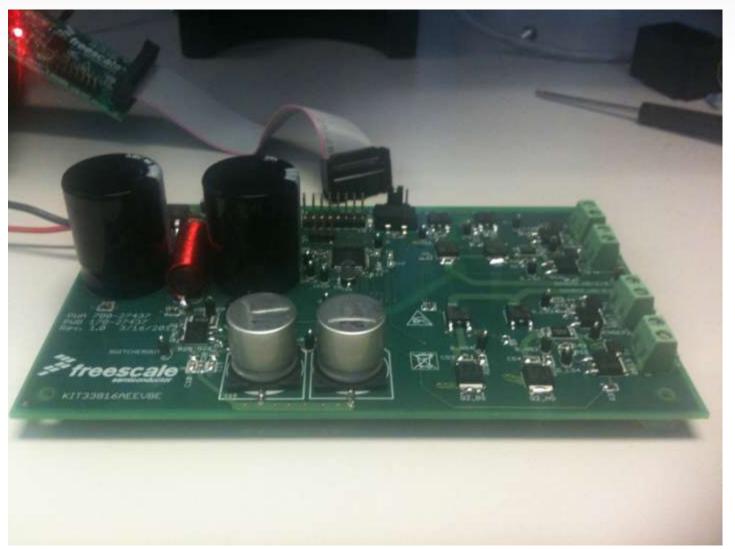

# MC33816 Evaluation Board (EVB)

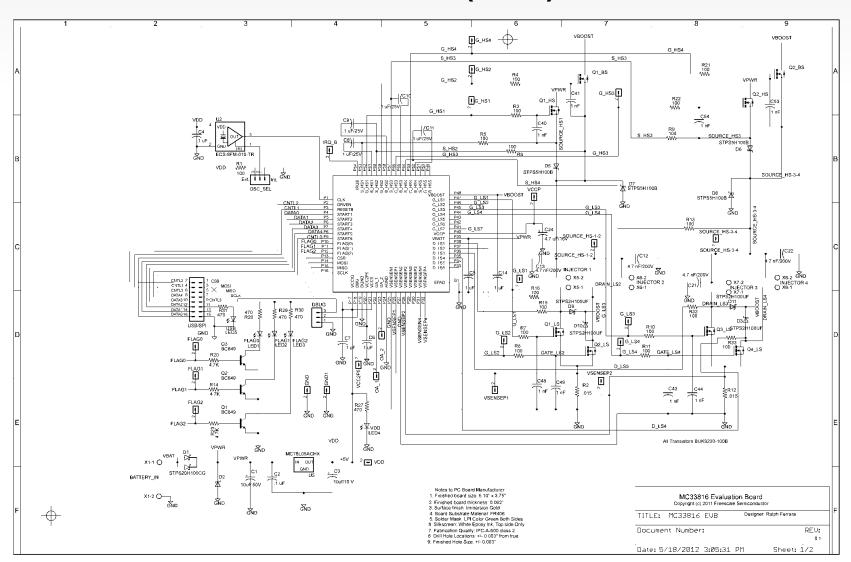

### MC33816 Evaluation Board (EVB) Schematic 1 of 2

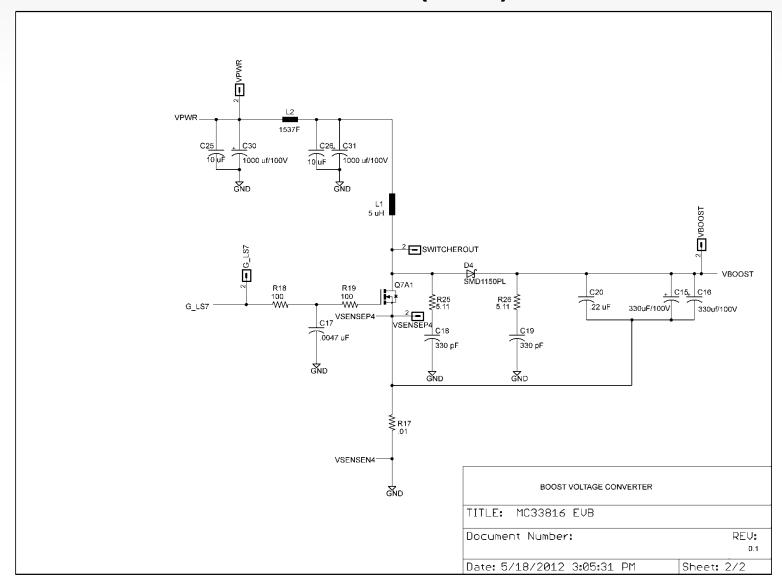

### MC33816 Evaluation Board (EVB) Schematic 2 of 2

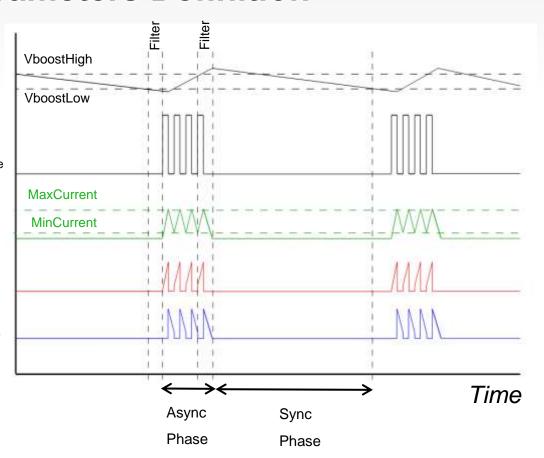

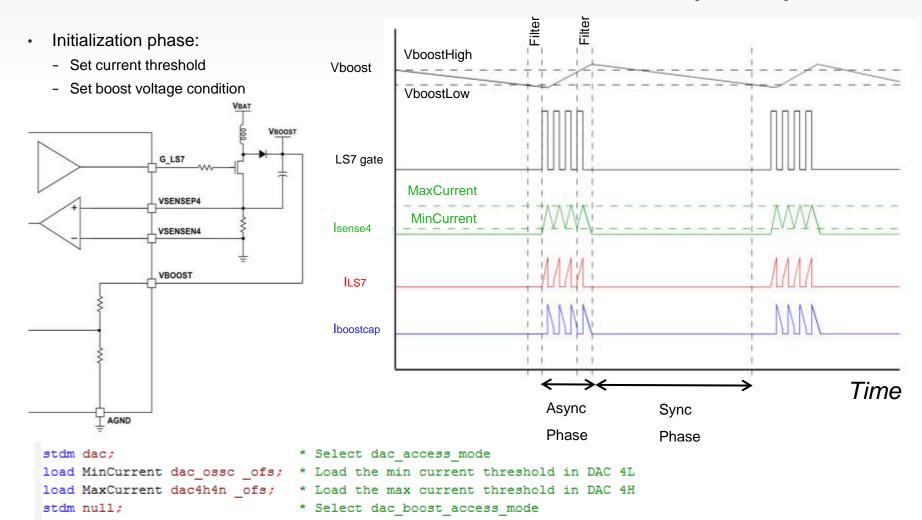

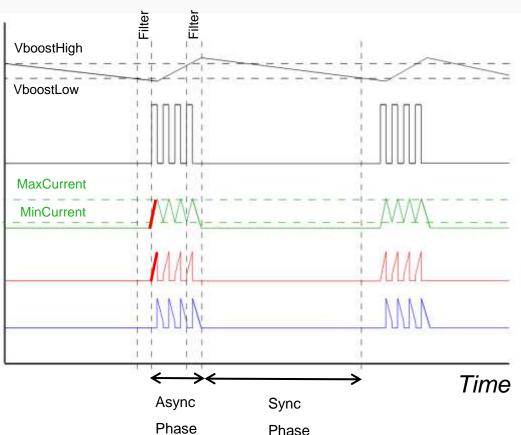

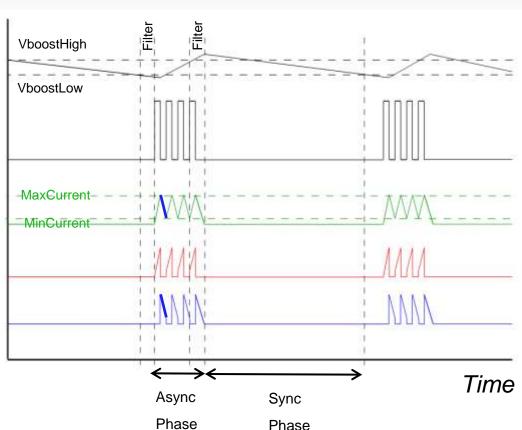

#### DC/DC Converter Parameters Definition

Hysteretic conversion mode: variable frequency

Vboost

Async Phase: current automatic regulation between MaxCurrent and MinCurrent up to Vboost>VboostHigh

LS7 gate

- Sync Phase: MOSFET off up to Vboost < VboostLow</li>

- MaxCurrent must be lower than the inductor saturation current

Isense4

Filter (usTime) is used to filter Vboost feedback ILS7

Iboostcap

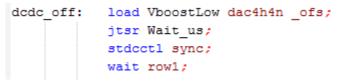

# DC/DC Converter Parameters Definition (con't)

cwer dcdc on vb row1;

cwer dcdc off vb row2;

\* Wait table entry for under threshold condition

\* Wait table entry for over threshold condition

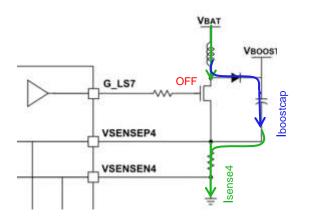

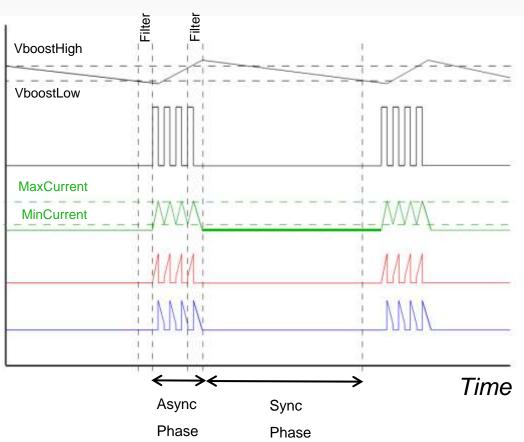

## DC/DC Converter: Async Phase

- LS7 is ON until Isense4 >MaxCurrent

- Current flowing through the inductor and the LS7 MOSFET

- Async phase up to Vboost>VboostHigh

VBOOST G LS7 ON ILS7 VSENSEP4 VSENSEN4

LS7 gate

sense4

boostcap

- load VboostHigh dac4h4n ofs; dcdc on: jtsr Wait us; stdcctl async; wait row2;

- \* Load the upper Vboost threshold in vboost dac register

- \* Wait here, mandatory due to long filter on boost voltage

- \* Enable HW PWM

- \* Wait for vboost over threshold condition

### DC/DC Converter: Async Phase (con't)

- LS7 is OFF until Isense4 < MinCurrent

- Current flowing through the diode and charging the capacitor

- Async phase up to Vboost>VboostHigh

Vboost

LS7 gate

Isense4

dcdc on: load VboostHigh dac4h4n ofs; jtsr Wait us; stdcctl asvnc; wait row2:

- \* Load the upper Vboost threshold in vboost dac register

- \* Wait here, mandatory due to long filter on boost voltage

- \* Enable HW PWM

- \* Wait for vboost over threshold condition

### DC/DC Converte: Sync Phase

Vboost

LS7 is OFF until Vboost < VboostLow</li>

- \* Load the upper Vboost threshold in vboost\_dac register

- \* Wait here, mandatory due to long filter on boost voltage

- \* Disable HW PWM

- \* Wait for vboost under threshold condition

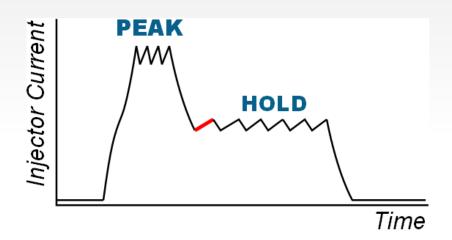

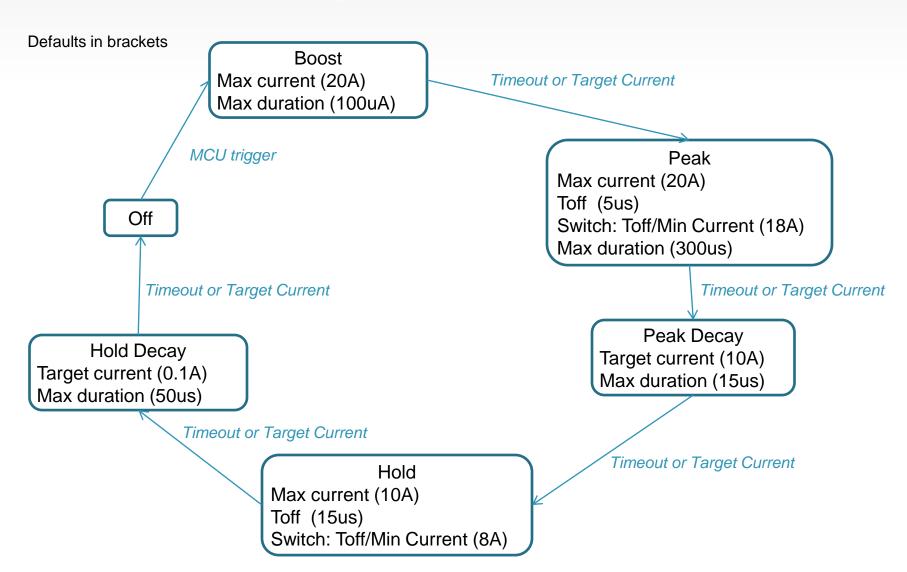

## Injector Current parameter definition

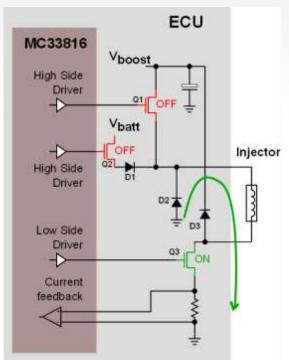

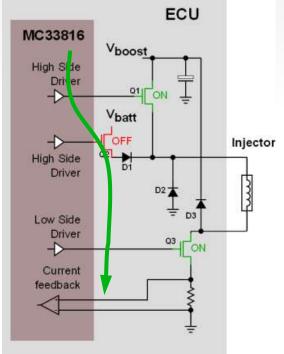

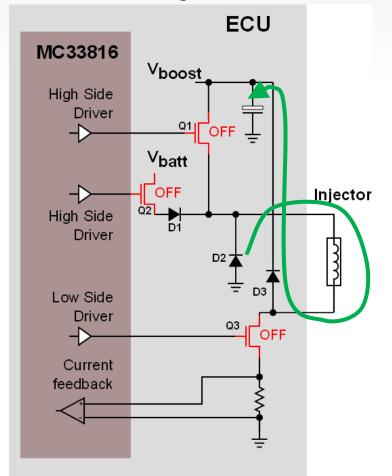

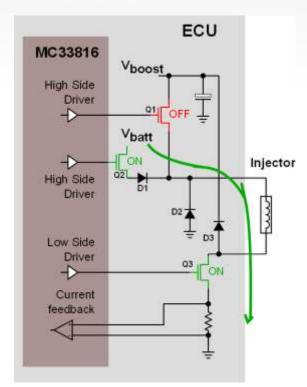

## Boosted, banked, direct injector architecture

- One injector shown.

- Common (banked) features are high side supplies and current feedback

- Individual cylinders get individual low side (LS) FETs

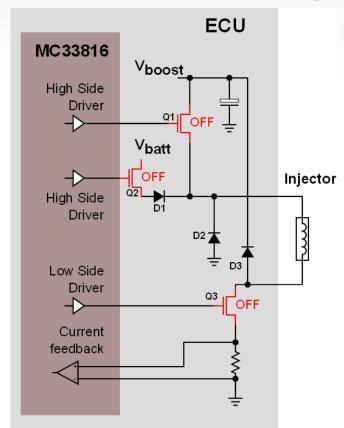

# Peak and hold sequencing: OFF state

- All FETs off

- No current flow

### Peak ON (Boost)

- Bank 1 Boost ON

- Inj1 HS Bat OFF

- Inj1 Low side ON

- Vbat blocked by diode D1

- Current rises to peak target

- \* Load the boost phase current threshold

- \* Jump to peak phase when current is over threshold

- \* If the start goes low, go to eoinj phase

- \* Turn VBAT off, BOOST on, LS on

- \* Wait for one of the 2 previously defined conditions

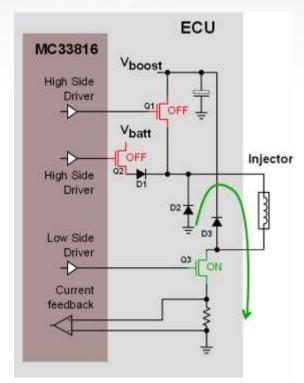

#### **Peak OFF**

- Bank 1 Boost OFF

- Inj1 HS Bat OFF

- Inj1 Low side ON

- Current recirculates through D2 and decays

- Peak phase is combination of Peak ON and Peak OFF

freescale™

```

*### peak phase continue on boost ###

ldcd rst ofs keep keep Tpeak tot c1;* Load the length of the total peak phase in counter 1

peak0:

* Jump to peak on when tc2 reaches end of count

cwer peak on0 tc2 row1;

* Jump to peak off when current is over threshold

cwer peak off0 ocur row2;

* Jump to off phase when tcl reaches end of count

cwer off phase0 tc1 row3;

load I peak dac sssc ofs;

* Load the peak current threshold

peak on0:

stos off on on:

* Turn VBAT off, BOOST on, LS on

wait row235;

* Wait for one of the previously defined conditions

1dcd rst ofs keep keep Tpeak off c2;* Load in the counter 2 the length of the peak off phase

peak off0:

* Turn VBAT off, BOOST off, LS on

stos off off on;

wait row135:

* Wait for one of the previously defined conditions

```

- Bank 1 Boost OFF

- Inj1 HS Bat OFF

- Inj1 Low side ON

- Current recirculates through D2 and decays

- Peak phase is combination of Peak ON and Peak OFF

```

*### peak phase continue on boost ###

ldcd rst ofs keep keep Tpeak tot c1;* Load the length of the total peak phase in counter 1

peak0:

* Jump to peak on when tc2 reaches end of count

cwer peak on0 tc2 row1;

* Jump to peak off when current is over threshold

cwer peak off0 ocur row2;

* Jump to off phase when tcl reaches end of count

cwer off phase0 tc1 row3;

load I peak dac sssc ofs;

* Load the peak current threshold

peak on0:

stos off on on;

* Turn VBAT off, BOOST on, LS on

wait row235;

* Wait for one of the previously defined conditions

1dcd rst ofs keep Keep Tpeak off c2;* Load in the counter 2 the length of the peak off phase

peak off0:

stos off off on:

* Turn VBAT off, BOOST off, LS on

wait row135;

* Wait for one of the previously defined conditions

```

#### Peak decay

- Bank 1 HS Boost OFF

- Bank 1 HS Bat OFF

- Inj1 LS OFF

- Current re-circulates through D2 and D3

- High voltage energy recovery to boost supply capacitor

- Faster decay rate than Peak OFF

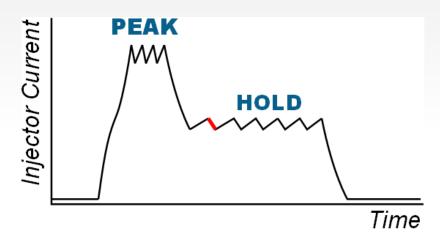

#### **Hold ON**

- Bank 1 HS Boost OFF

- Bank 1 HS Bat ON

- Inj1 LS ON

- Current rises to hold target

```

*### hold phase on Vbat ###

ldcd rst _ofs keep keep Thold_tot c2;* Load the length of the total hold phase in counter 2

hold0:

load I_hold dac_sssc _ofs;

* Load the hold current threshold in the DAC

cwer hold off0 ocur row1;

* Jump to hold off when current is over threshold

cwer hold_on0 tc1 row2;

* Jump to hold_on when tc1 reaches end of count

cwer eoinj0 tc2 row3;

* Jump to eoinj when tc2 reaches end of count

hold on0:

stos on off on;

* Turn VBAT on, BOOST off, LS on

wait row135;

* Wait for one of the previously defined conditions

hold off0: ldcd rst ofs keep keep Thold off c1;* Load the length of the hold off phase in counter 1

stos off off on;

* Turn VBAT off, BOOST off, LS on

wait row235:

* Wait for one of the previously defined conditions

```

#### **Hold OFF**

- Same as Peak OFF

- Bank 1 HS Boost OFF

- Bank 1 HS Bat OFF

- Inj1 LS ON

- · Current re-circulates through D2 and decays

- Hold phase is combination of Hold ON and Hold OFF

```

*### hold phase on Vbat ###

hold0:

ldcd rst _ofs keep keep Thold_tot c2;* Load the length of the total hold phase in counter 2

load I_hold dac_sssc _ofs;

* Load the hold current threshold in the DAC

cwer hold off0 ocur row1;

* Jump to hold off when current is over threshold

cwer hold_on0 tc1 row2;

* Jump to hold_on when tc1 reaches end of count

cwer eoinj0 tc2 row3;

* Jump to eoinj when tc2 reaches end of count

* Turn VBAT on, BOOST off, LS on

hold on0:

stos on off on;

wait row135;

* Wait for one of the previously defined conditions

hold_off0: ldcd rst _ofs keep keep Thold_off c1;* Load the length of the hold_off phase in counter 1

stos off off on;

* Turn VBAT off, BOOST off, LS on

wait row235:

* Wait for one of the previously defined conditions

```

#### **End of Injection**

- Same as Peak Decay

- Bank 1 HS Boost OFF

- Bank 1 HS Bat OFF

- Inj1 LS OFF

- Current re-circulates through D2 and D3

- High voltage energy recovery to boost supply capacitor

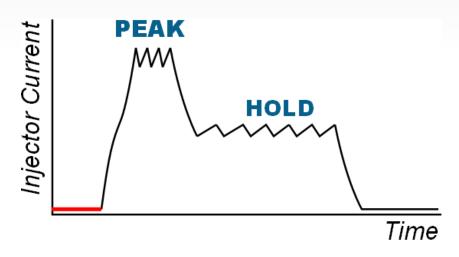

### Peak and hold programmable parameters

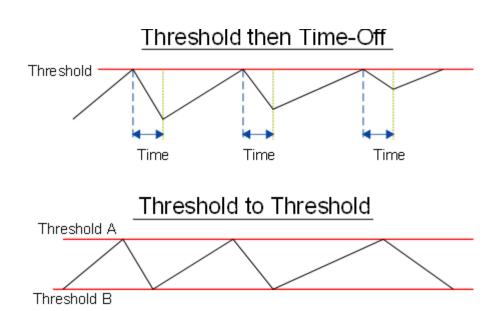

#### Software routines

- Manage transitions. Current may be above or below threshold on entry, use appropriate state ON or OFF

- Option on current control:

- Threshold then Toff

- Threshold to threshold (Current measurement 4 only)

## Implementation on ECU

- Currents and default durations programmed over SPI

- Start signal from MCU rising triggers start of injection pulse

- Start signal from MCU triggers end of HOLD phase

#### Channels required for EVB

- High side Boost supply FET with PWM

- Two on EVB

- High side Battery supply FET with PWM

- Two on EVB

- Low side FET with PWM

- Four on EVB

- Current sense low side channel

- Four on EVB

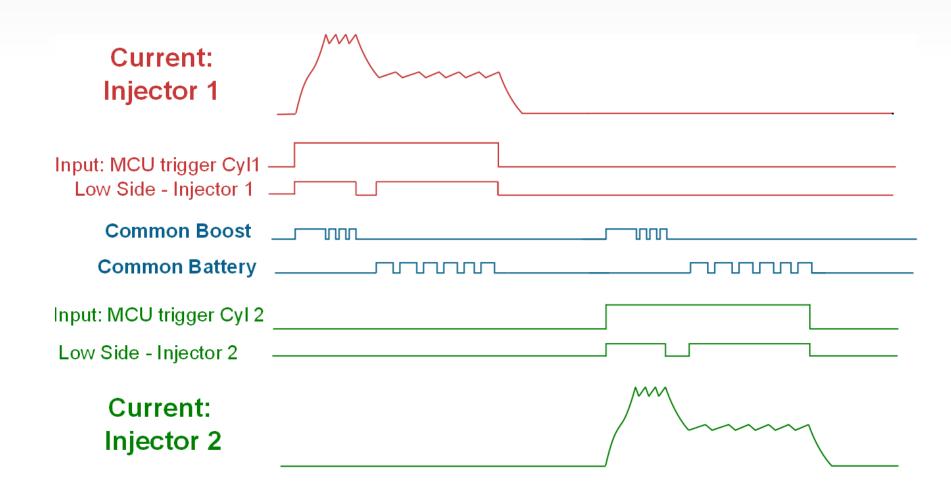

#### Waveforms: banked mode

## Agenda

- Purpose for introducing the MC33816

- Overview of MC33816

- Hardware Circuit functions and features

- Software Instruction set and tools

- MC33816 Applications and Examples

- 4 and 6 cylinder examples

- Peak and Hold waveform generation

- Boost voltage regulator

#### **Thank You!**

For more information see the following additional slides or contact the authors.

Tag yourself in photos and upload your own!

Tweeting?

Please use hashtag

#FTF2012

Session materials will be posted @ www.freescale.com/FTF Look for announcements in the FTF Group on LinkedIn or follow Freescale on Twitter

Additional Backup Slides and Information

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, CorlQ, Oorivva, StarCore. Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, MagniV, MXC, Platform in a Package, OorlQ Oonverge, QUICC Engine, Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @ 2012 Freescale Semiconductor, Inc.

## **Additional Backup Slides and Information**

- Diagnostics and FMEN

- Flag Configuration Details

- Instructions Detailed Description

### **Diagnostics and FMEM #1**

- Boost FET

- Open: report, leave FET on

- Short to Vbat: report, turn FET off and retry next event

- Short to Gnd: report, turn FET off and retry next event

- Battery FET

- Open: report, leave FET on

- Short to Vbat: report, leave FET on

- Short to Gnd: report, turn FET off and retry next event

- Low side FET

- Open: report, leave FET on

- Short to Vbat: report, turn FET off and retry next event

- Short to Gnd: report, leave FET on

## Diagnostics and FMEM #2

- Failure to reach Boost voltage: report and continue

- Failure to reach target current in prescribed duration (any phase):

report and continue

# **Additional Backup Slides and Information**

- Diagnostics and FMEN

- Flag Configuration Details

- Instructions Detailed Description

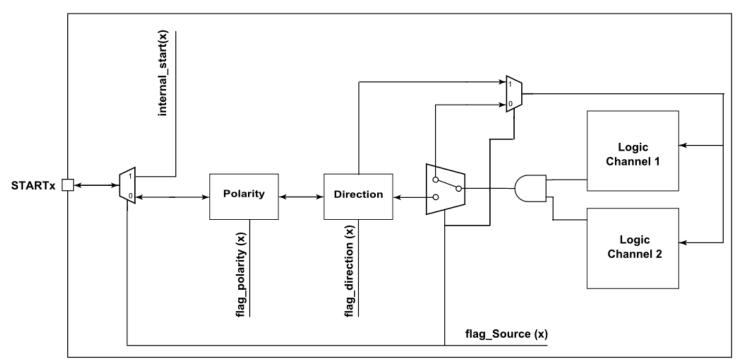

# Flags 3 to 8 (STARTx pins)

- Can be connected to the STARTx pins (digital input pins)

- ✓ Can provide direct digital inputs to the µCores (programmable)

- ✓ Set as output combination of the Logic Channels 1 and 2 local flags

- Set as internal flag the STARTx pin keep their primary functions.

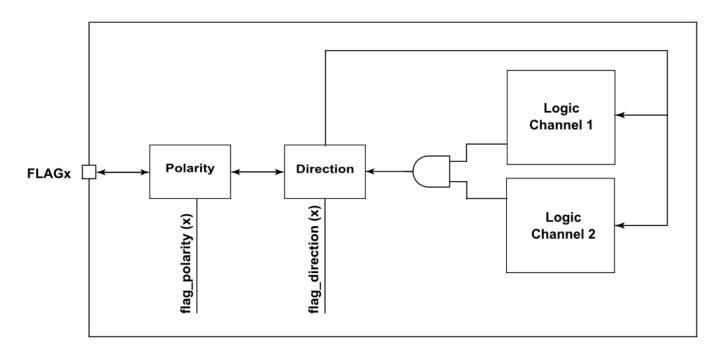

## Flag 0 to Flag 2 (FLAGx pins)

- Always connected to FLAGx pins (digital input pins)

- ✓ Set as input directly feedbacks the µCores

- Set as output combination of the Logic Channels 1 and 2 'local' flags

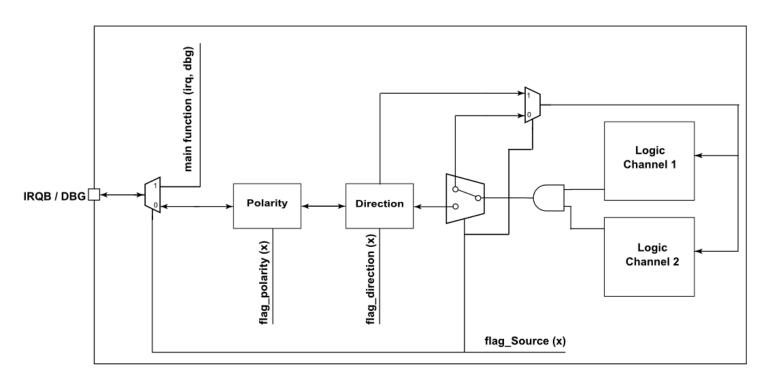

## Flag 9 and Flag 12 (pins IRQB and DBG)

- ✓ Can be connected to the IRQB and DBG pins (digital pins)

- ✓ Set as input directly feedbacks the µCores

- Set as output combination of the Logic Channels 1 and 2 'local' flags

- ✓ Set as internal flag the STARTx pin keep their primary functions.

## Flag 10 and Flag 11 (pins OA\_x)

- ✓ Can be connected to the OA\_x pins (analog output pins)

- ✓ Set as input directly feedbacks the µCores

- ✓ Set as output combination of the Logic Channels 1 and 2 'local' flags

- ✓ Set as internal flag the OA\_x pin keep their primary functions.

## Flag 13 to Flag 15

Internal flags only

## **Additional Backup Slides and Information**

- Diagnostics and FMEN

- Flag Configuration Details

- Instructions Detailed Description

#### **Software - Instruction Set Overview**

- √ 93 instructions in 7 categories:

- 1. Arithmetic Logic Unit (27)

- 2. Configuration (29)

- 3. Diagnostic (3)

- 4. Interrupt and Subroutine (6)

- 5. Jump (16)

- 6. Load (9)

- 7. Wait (3)

## 27 Arithmetic Logic Unit (ALU) Instructions

- 1. add addition of two registers

- addi addition with immediate register

- *and* mask AND with immediate register

- *a. mul* multiplication of two registers

- 5. muli multiplication with immediate value

- 6. **not** invert contents of a register

- 7. **or** mask OR with immediate register

- 8. **sub** subtraction of two registers

- subi subtraction with immediate register

- 10. swap swap high and low bytes of a register

- 11. toc2 performs 2's complement on register

- 12. toint converts 2's complement to integer

- *13.* **xor** mask XOR with immediate register

# 27 ALU Instructions (con't)

- 14. sh32l shift 32-bit register left (register)

- 15. sh32li shift 32-bit register left immediate

- *sh32r* shift 32-bit register right (register)

- 17. sh32ri shift 32-bit register right immediate

- **18. shl** shift register left (register)

- 19. shl8 shift register left 8 positions

- 20. shli shift register left immediate

- 21. **shls** shift register left signed (register)

- 22. **shlsi** shift register left signed immediate

- **23. shr** shift register right (register)

- **24. shr8** shift register right 8 positions

- 25. shri shift register right immediate

- **26. shrs** shift register right signed (register)

- 27. shrsi shift register right signed immediate

#### **ALU Instructions: Addition and Subtraction**

The ALU contains a single-cycle 16-bit adder. Overflow and underflow are managed according to the configuration called *arithmetic\_logic*.

#### Instruction "stal arithLogic":

- Set the ARITH\_LOGIC(1:0) bits of the ALU configuration register:

- all, C2: number are considered to be 2-complement. Overflow limit is 0x7FFF, underflow limit is 0x8000.

- a12, C2sat: number are considered to be 2-complement. Overflow limit is 0x7FFF, underflow limit is 0x8000. In case of overflow the result is saturated to 0x7FFF, in case of underflow the result is saturated to 0x8000.

- al3, Pos: number are considered to be positive. Overflow limit is 0xFFFF, underflow limit is 0x0000.

- al4, PosSat: number are considered to positive. Overflow limit is 0xFFFF, underflow limit is 0x0000. In case of overflow the result is saturated to 0xFFFF, in case of underflow the result is saturated to 0x0000.

#### Condition register bits affected:

ARITH\_LOGIC (12-11)

## **ALU Instructions: Addition and Subtraction (con't)**

```

Instruction "add op1 op2 res":

```

Reg[res] = Reg[op1] + Reg[op2]

Instruction "addi op1 immediate res":

Reg[res] = Reg[op1] + imm

Instruction "sub op1 op2 res":

Reg[res] = Reg[op1] - Reg[op2]

Instruction "subi op1 immediate res":

Reg[res] = Reg[op1] - imm

#### Condition register bits affected:

CARRY (13), RES\_ZERO (6), RES\_SIGN(5), UNSIGNED\_UND (4), UNSIGNED\_OVR (3), SIGNED\_UND (2), SIGNED\_OVR (1)

Note: The operand 'imm' is a 4-bit immediate value a an direct instruction parameter.

# **ALU Instructions: Multiplication (con't)**

The ALU contains a single-cycle 16-bit x 16-bit multiplier. The multiplier produces a 329-bit result, so overflow is not possible. The result is correct only if the operands are represented as positive numbers. The result is available after 32 clock cycles.

Instruction "mul op1 op2":

m = Reg[op1] \* Reg[op2]

Instruction "muli op1 immediate":

GPR6 & GPR7 = Reg[op1] \* imm

# Condition register bits affected:

MUL\_SHIFT\_OVR (8), MUL\_SHIFT\_LOSS (7), OP\_DONE (0)

## **ALU Instructions: Multiplication (con't)**

To multiply 2-complement represented numbers, they must first be converted to positive representation.

```

Instruction "toint op1 rst":

```

• Extract the module from a 2-complement represented number. The sign can either replace or be accumulated in the CONV\_SIGN bit. The operation consumes the operand.

#### Instruction "toc2 op1":

- Convert the operand from positive to 2-complement representation by adding the sign contained in the CONV SIGN bit.

- Example:

#### Condition register bit affected:

CONV\_SIGN (14)

#### **ALU Instructions: Shift**

The result of these shift operation is available after a number of clock cycles equal to the number of shift positions required.

Instruction "shr op1 op2":

Reg[op1] = Reg[op1] >> Reg[op2]. The bits shifted in are all '0'.

Instruction "shl op1 op2":

Reg[op1] = Reg[op1] << Reg[op2]. The bits shifted in are all '0'.</li>

Instruction "shri op1 immediate":

Reg[op1] = Reg[op1] >> immediate. The bits shifted in are all '0'.

Instruction "shli op1 immediate":

Reg[op1] = Reg[op1] << immediate. The bits shifted in are all '0'.</li>

#### ALU Condition register bits affected:

SHIFT\_OUT (15), OP\_DONE (0)

## **ALU Instructions: Shift (con't)**

The result of these shift operation is available after a number of clock cycles equal to the number of shift positions required. In all these instruction the MSB is not shifted.

Instruction "shrs op1 op2":

Reg[op1] = Reg[op1] >> Reg[op2]. The bits shifted in are equal to the MSB.

Instruction "shls op1 op2":

Reg[op1] = Reg[op1] << Reg[op2]. The bits shifted in are all '0'.</li>

Instruction "shrsi op1 immediate":

Reg[op1] = Reg[op1] >> immediate. The bits shifted in are equal to the MSB.

Instruction "shlsi op1 immediate":

Reg[op1] = Reg[op1] << immediate. The bits shifted in are all '0'.</li>

#### ALU Condition register bits affected:

SHIFT\_OUT (15), OP\_DONE (0)

## **ALU Instructions: Shift (con't)**

The result of these shift operation is available after a number of clock cycles equal to the number of shift positions required. These instructions operate only on the 32-bit register.

Instruction "sh32r op1":

m = mh & ml >> Reg[op1]. The bits shifted in are all '0'.

Instruction "sh321 op1":

m = mh & ml << Reg[op1]. The bits shifted in are all '0'.</li>

Instruction "sh32ri immediate":

m = mh & ml >> immediate. The bits shifted in are all '0'.

Instruction "sh32li immediate":

m = mh & ml << immediate. The bits shifted in are all '0'.</li>

#### ALU Condition register bits affected:

SHIFT\_OUT (15), OP\_DONE (0)

## **ALU Instructions: Shift (con't)**

These operations are all single cycle. Useful for 8 bit operations.

Instruction "sh8r op1":

Reg[op1] = Reg[op1] >> 8. The bits shifted in are all '0'.

Instruction "sh81 op1":

Reg[op1] = Reg[op1] << 8. The bit shifted in are all '0'.</li>

Instruction "swap op1":

• Reg[op1] = (Reg[op1] << 8) + (Reg[op1] >> 8).

#### ALU Condition register bits affected:

None

# **ALU Instructions: Logic operations**

Logic operations always consumes the operand. If a mask is needed, the immediate register is used (r5).

Instruction "not op1":

Every bit of Reg[op1] is inverted.

Instruction "and op1":

Reg[op1] = Reg[op1] & r5.

Instruction "or op1":

Reg[op1] = Reg[op1] | r5.

Instruction "xor op1":

Reg[op1] = Reg[op1] ^ r5.

#### Condition register bits affected:

MASK\_MIN(10), MASK\_MAX (9)

#### **Software - Instruction Set Overview**

- √ 93 instructions in 7 categories:

- 1. Arithmetic Logic Unit (27)

- 2. Configuration (29)

- 3. Diagnostic (3)

- 4. Interrupt and Subroutine (6)

- 5. Jump (16)

- 6. Load (9)

- 7. Wait (3)

## 29 Configuration Instructions

- 1. bias enables/disables a single bias structure

- 2. **chth** changes threshold on feedback comparator

- 3. **dfcsct** define shortcut for current feedback

- *dfsct* define shortcut for outputs

- 5. rdspi request SPI read

- *c. rstreg* reset register

- 7. **rstsl** reset start latch register

- 8. slab select address base

- slfbk- select feedback source

- 10. slsa selects which register to use as SPI address

- 11. stab load value in address base register

- 12. stadc enables/disables ADC conversion on specified current measurement block

## 29 Configuration Instructions (con't)

- 13. stal set ALU mode (ARITH\_LOGIC(1:0) bits )

- 14. **stcrb** set control register bit

- 15. stcrt set channel communication register

- 16. **stdcct** set DC/DC control mode

- 17. stdm set DAC register access mode

- 18. **stdrm** set DRAM read mode

- 19. **steoa** enable end of actuation mode

- **20. stf** set flag

- 21. **stfw** set freewheeling mode

- 22. stgn set Op Amp gain

- 23. stirq set interrupt request output pin

- 24. sto set single output

- **25. stoc** set offset compensation

- **26. stos** set output shortcut

# 29 Configuration Instructions (con't)

- 27. stslew set slew rate

- 28. stsrb set status register bit

- 29. wrspi— request SPI write (backdoor)

#### Bias, Threshold and Slewrate Instructions

The action of all these instructions is masked by the "output\_access" register of the µCore.

#### Instruction "bias sel ctrl":

- Biasing can be configured as described below.

- a single bias structure

- all HS bias structures

- all LS bias structures

- all bias structures

#### Instruction "stslew sel":

Force or unforce the value of the slewrate to the maximum value.

#### Instruction "chth sel level":

Set the threshold of a voltage feedback comparator.

# Internal Registers and Data RAM

Instruction "stab addrbase":

Set the Data RAM Address Base.

Instruction "slab sel":

Force the ALU GPR5 (immediate register) as Data RAM offset instead of the Address Base. By default the Address Base is used.

# Onfiguration Instructions: Internal Registers and Data RAM (con't)

#### Instruction "stdrm sel":

- Select the "data ram read mode" per the combinations below:

- word: when a "load" instruction is executed, all the 16 bit of the data ram value are written in the destination register. This is the default value.

- lowbyte: when a "load" instruction is executed, all the 8 LSBs of the data ram value are written in the 8 LSBs of the destination register. The 8 MSBs of the destination register are filled with '0'.

- highbyte: when a "load" instruction is executed, all the 8 MSBs of the data ram value are written in the 8 LSBs of the destination register. The 8 MSBs of the destination register are filled with '0'.

- swapbyte: when a "load" instruction is executed, all the 8 MSBs and the 8 LSBs of the data ram value are written swapped in the destination register.

### Configuration Instructions: SPI 'Backdoor'

Reading or writing an SPI accessible register always requires a multi-instruction set.

#### Instruction "slsa sel":

Select if the address to be used for the operation is spi\_add or GPR5. By default the address used is spi\_add.

#### Instruction "rdspi":

Read the SPI register at the address 0x100 + the selected address. The result is available at in the register spi\_data.

#### Instruction "wrspi":

Write the value contained in the internal register spi\_data into the SPI register at the address

0x100 + the selected address.

#### **Shortcut Instructions**

In order to optimize the code size 3 output shortcuts and 1 current feedback shortcut can be defined.

#### Instruction "dfcsct short":

- Define one of the current feedback as shortcut. For this purpose, only current feedbacks 1 to 4L can be selected (define 4H and 4Neg is not allowed). The instructions that can use the current feedback defined as shortcut are:

- conditional jump/wait on feedbacks ("jocr/f", "cwer/f") (own current feedback high/low)

#### Instruction "dfsct short1 short2 short3":

- Define up to 3 output shortcuts. More than 1 shortcut can point to the same output.

The instructions that can use the output defined as shortcuts are:

- load complex ("ldcd", "ldca")

- set output shortcuts ("stos")

- jump/wait condition on feedbacks ("jocr/f", "cwer/f")

## **Status and Control Registers Instructions**

The status register is 16-bit wide. It can be read/written by the µCore, while the external micro-controller can only read this register through SPI.

The register can be used as an output communication channel towards an external device or as temporary register. A combination of the two is possible.

#### Instruction "stsrb value sel":

- Set the value of one of the bits of the status register.

- The status register can be read/written as a word (using "cp", "load" or "store") or a single bit test (using "jsrr/f").

## Status and Control Registers Instructions (con't)

The control register is made of two 8-bit part:

- CR[7:0], can only be read by the µCore, while the external micro-controller can read

or write this slice. This slice can be used as an input communication channel from an

external device.

- CR[15:8] have a configurable behavior. This slice can be used like either the lower slice (CR[7:0]) or as the status register.

#### Instruction "stcrb value sel":

Set the value of one of the bits of the upper slice of the control register. This

operation is successful only if the slice is configured to behave like the status register.

The control register can be read as a whole (using "cp", "load" or "store") or a single bit can be tested (using "jcrr/f"), regardless of the configuration of the CR[15:8] slice.

# **Configuration Instructions: Flags Instructions**

• The channel flags can be set all at once with the cp or load instructions, one at time with the stf instruction.

#### Instruction "stf value sel":

- Set the value of one of channel flags.

- The flags can be read as a whole (using "cp" or "store") or a single bit can be tested (using "jocr/f" or "cwer/f").

# **Configuration Instructions: Output Drivers**

The outcome of all these instructions is masked by the "output\_access" registers of the µCore.

Instruction "sto sel outValue":

Set the status of a single output driver.

Instruction "stos outValue1 outValue2 OutValue3":

Set the status of the outputs defined as shortcuts.

Instruction "ldcd rst ofs outValue1 outValue2 counter address":

Load a counter from Data DAM and set the outputs defined as shortcut1 and shortcut2.

Instruction "ldca rst outValue1 outValue2 counter address":

Load a counter from an ALU register and set the outputs defined as shortcut1 and shortcut2

# Configuration Instructions: Output Drivers (con't)

Each HS MOSFET can be configured as automatic free function. There are 5 pre-defined pairing HS-FW drivers implemented.

#### Instruction "stfw mode":

This instruction is effective only if the output shortcut 1 is an HS, and if the μCore has

the access right to drive the FW mosfet related to that HS. In this case, the instruction

activates or deactivates automatic FW driving for that HS-FW pair.

# Configuration Instructions: Output Drivers (con't)

#### Instruction "stdcctl mode":

The LS7 can be switched from the default synchronous mode (output driven by one of the

μCores), to asynchronous mode. In this condition it is completely independent from the code flow

and its output value is determined only by the unfiltered current feedbacks.

### Instruction "steoa diag mode":

Activate end of actuation mode (used to measure when the current reaches 0A) for all the HS for which the µCore has access rights. It can also enable or disable the diagnosis on the related Vsource comparators.

# **Configuration Instructions: DAC**

#### 7 registers are dedicated to DACs

- 4 are managed independantly –Dac4h, Dac4neg and Boost\_dac are managed as a group

- R/W access using "cp", "load" and "store"

- The instructions is masked by the "current\_access" register of the μCore.

- The value 15 corresponds to 0A threshold. Lower is a negative threshold, higher is positive.

| Address (Hex) | Description   |

|---------------|---------------|

| 19B           | Boost_dac     |

| 19E           | Dac1_value    |

| 19F           | Dac2_value    |

| 1A0           | Dac3_value    |

| 1A1           | Dac4l_value   |

| 1A2           | Dac4h_value   |

| 1A3           | Dac4neg_value |

#### Instruction "stdm sel":

• Select the "dac mode". It can be null, dac(default), offset or full.

# onfiguration Instructions: Current Measurement Control

The action of all these instructions is masked by the "current\_access" register of the µCore.

Instruction "stgn target value":

Set the gain of the operational amplifier of one of the current measure blocks.

Instruction "stade target mode":

Enable or disables adc mode on one of the current measure blocks. While the mode

is active, the acquired value can be read (with "cp" or "store") in the internal

memory map at the address normally used for the corresponding DAC.

Instruction "stoc target mode":

Enable or disables automatic offset compensation on one of the current measure blocks. This mode should be active only if the differential input of the current measure block is zero.

# Communication Register

Each of the four  $\mu$ Core s has a "channel communication register" (CCR), useful to exchange 16-bit data between different  $\mu$ Cores. When this register is written ("cp" or "load"), the  $\mu$ Core writes its own register. When the register is read ("cp" or "store"), the  $\mu$ Core can read its own or the one belonging to another  $\mu$ Core.

## Instruction "stcrt seqId":

Configures a link between the μCore and the CCR of another μCore. It is used when the CCR is read. It is possible to link a μCore with his own CCR, to use the CCR a temporary register.

# **Configuration Instructions: Interrupts**

### Instruction "rstreg target":

- This instruction can reset one or more of the following register.

- Status register. It includes the higher slice of the control register, if it is configured to behave like the status register.

- Control register. The upper slice is excluded if it is configured to behave like the status register.

- Automatic diagnosis register, thus enabling latching the status of the output drivers when the next fault occurs.

- Automatic diagnosis interrupt generation. Re-enables the generation of interrupt from the automatic diagnosis block.

### Instruction "slfbk mode diag":

HS2 and HS4 have 2 different Vds comparator each, one which uses Vboost pin as drain, the other which uses Vbat pin as drain. This pin selects which is the enabled comparator between the 2 and can enable or disable the diagnosis on that comparators.

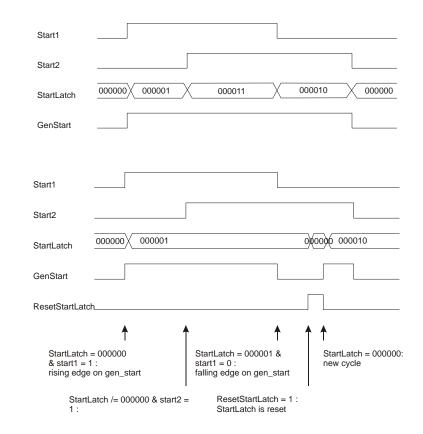

# **Configuration Instructions: Start Management**

The 6 start signals can be used to trigger the actuations but each  $\mu$ Core can access only a configurable subset of these signals: gen\_start and start\_latch. The generation of these signals depend of the start mode selected. Each of the 4  $\mu$ Core has its own gen\_start and start\_latch signals set.

#### Normal start mode:

- gen\_start : logical "OR" of all the accessible start signals.

- start\_latch: 'living copy' of all the accessible start signals.

#### Smart start mode:

- gen\_start: active when one of the start is active and start\_latch is zero. Deactivated when the start that triggered its rising edge goes low.

- start\_latch saves the status of the starts if one

of the accessible start signal is active and the

previous value of start\_latch is zero. The

start\_latch is reset when the "rstsl"

instruction is executed.

#### Instruction "rstsl":

•Reset the start\_latch, enabling theenablement to other start signals.

## **Software - Instruction Set Overview**

- √ 93 instructions in 7 categories:

- 1. Arithmetic Logic Unit (27)

- 2. Configuration (29)

- 3. Diagnostic (3)

- 4. Interrupt and Subroutine (6)

- 5. Jump (16)

- 6. Load (9)

- 7. Wait (3)

# **3 Diagnostic Instructions**

- endiag enable diagnostics (single)

- endiaga enable diagnostics (all)

- 3. endiags enable diagnostic shortcut

## **Software - Instruction Set Overview**

# √ 93 instructions in 7 categories:

- 1. Arithmetic Logic Unit (27)

- 2. Configuration (29)

- Diagnostic (3)

- **Interrupt and Subroutine (6)**

- **Jump (16)**

- 6. Load (9)

- 7. Wait (3)

# 3 Interrupt Instructions

- 1. iconf interrupt configuration

- *iret* return from interrupt

- *reqi* request for software interrupt

# **Interrupt Intructions: Concept**

#### Each µCore has 3 interrupt sources:

- automatic diagnostics. It can be enabled/disabled through SPI registers and instructions.

- driver disabled or loss of clock. It can be enabled/disabled through SPI register.

- **software interrupt**. It includes **gen\_start** rising and falling edge. The software interrupts related to **gen\_start** can be enabled/disabled through SPI registers, the others must be requested by an instruction.

- When an interrupt is received, the code execution is halted and the corresponding interrupt routine is executed (address in Channel Parameter Register).

- All interrupt routines cannot be interrupted by other interrupts. Interrupts received during this state are cached and can be serviced after the end of the currently executing routine.

- The interrupt service routine is ended by an "iret" instruction.

## **Interrupt Intructions**

#### Instruction "iconf mode":

- It configures the μCore enablement by automatic interrupt return request.

- none: automatic interrupt return request are ignored.

- restart: if a matching automatic interrupt return request is received, the interrupt routine ends and the code execution restart from the entry point.

- continue: if an matching automatic interrupt return request is received, the interrupt routine ends and the code execution resume from the value saved in the irq\_status register.

#### Instruction "iret dest rst":

- It ends the interrupt service routine. It is possible to reset the irq buffer. The code execution continues according to the dest parameter:

- restart: the code execution restarts from the entry point.

- continue: the code execution resumes from the value saved in the irq status register.

## **3 Subroutine Instructions**

- 1. jtsf jump to subroutine far

- jtsr jump to subroutine relative

- 3. **rfs** return from subroutine

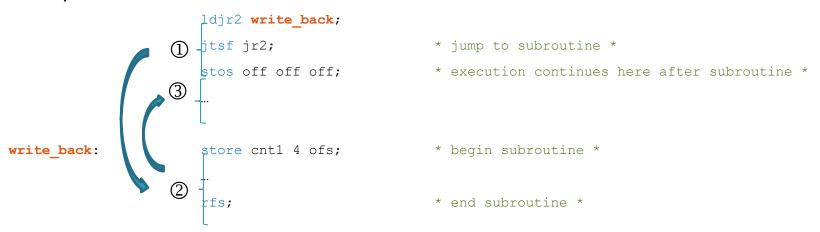

## Flow Control Instructions: Subroutine

## Instruction "jtsr/f dest":

Begin the subroutine at the specified address. The return address is saved into the "auxiliary" register.

#### Instruction "rfs":

• End the interrupt routine. Code execution resumes at the value saved into the auxiliary register + 1. Return address can be manipulated.

#### Example:

## **Software - Instruction Set Overview**

- √ 93 instructions in 7 categories:

- 1. Arithmetic Logic Unit (27)

- 2. Configuration (29)

- 3. Diagnostic (3)

- 4. Interrupt and Subroutine (6)

- 5. Jump (16)

- 6. Load (9)

- 7. Wait (3)

## 16 Jump Instructions

- 1. **jarf j**ump on **a**rithmetic **r**egister **f**ar

- 2. **jarr j**ump on **a**rithmetic **r**egister **r**elative

- 3. jcrf jump on control register far

- 4. jcrr jump on control register relative

- 5. jfbkf jump on feedback far

- 6. jfbkr jump on feedback relative

- 7. **jmpf** unconditional **jump** far

- 8. **jmpr** unconditional **jump** relative

- 9. **jocf j**ump **o**n flag **c**ondition **f**ar

- 10. **jocr j**ump **o**n flag **c**ondition **r**elative

- 11. joidf jump on μcore id far

- 12. **joidr j**ump **o**n μcore **id r**elative

- 13. joslf jump on start-latch far

# 16 Jump Instructions (con't)

- 14. joslr jump on start-latch relative

- 15. jsrf jump on status register far

- 16. jsrr- jump on status register relative

# **Jump Instructions: Test Conditions**

- ✓ Flags (high or low)

- ✓ Internal counters

- ✓ Start trigger signals (high or low)

- ✓ Voltage feedback signals (high or low)

- ✓ Boost voltage feedback signals (high or low)

- ✓ Current feedback signals (high or low)

- ✓ ALU condition register bits

- ✓ Status register bits (internal status) (high or low)

- ✓ Control register bits (commands from microcontroller) (high or low)

- ✓ µCore ID (test for a specific version of µCore)

# Jump Instructions: Code RAM addressing modes

#### ✓ Relative addressing (-r):

- The Code line address is expressed as an offset (-16 and 15 lines) relative to the current code line

- The operation requires only 1 instruction only and is preferred when applicable.

- Example:

#### Absolute addressing (-f):

- The code line address is expressed as an absolute value (10 bits)

- The value must be pre-charged into a jump register (jr1 or jr2)

- The operation requires 2 instruction must be used if relative addressing is not applicable

- Example:

#### Instruction "ldjr1/2 address":

Load the address parameter into one of the jump registers.

# Jump Instructions (con't)

Instruction "jmpr/f dest":

Unconditional jump.

Instruction "jarr/f dest sel":

Jump using a bit of the arithmetic register as condition.

Instruction "jcrr/f dest sel value":

Jump using a bit of the control register as condition.

Instruction "jsrr/f dest sel value":

Jump using a bit of the status register as condition.

Instruction "jfbkr/f dest sel value":

Jump using one of voltage feedbacks as condition

Instruction "joslr/f dest value":

Jump if the start latch has the required value

Instruction "joidr/f dest value":

Jump if the µCore id is the required one

## **Software - Instruction Set Overview**

- √ 93 instructions in 7 categories:

- 1. Arithmetic Logic Unit (27)

- 2. Configuration (29)

- 3. Diagnostic (3)

- 4. Interrupt and Subroutine (6)

- 5. Jump (16)

- 6. Load (9)

- 7. Wait (3)

## 9 Load Instructions

- 1. **cp** copy source to destination register

- 2. Idca load counter from register and set outputs

- 3. **Idcd** load counter from DRAM and set outputs

- 4. **Idirh** load immediate register high-byte

- 5. Idirl— load immediate register low-byte

- Idjr1 load jump register 1

- 7. **Idjr2** load jump register 2

- 8. **load** load data from DRAM to register

- store— store data from register to DRAM

# Load Instructions: Internal Registers and Data RAM

Instruction "cp source dest":

Copy the value from a register to another, both of which must be in the internal memory map.

Instruction "load source dest ofs":

Copy the value from the Data RAM to a register in the internal memory map. For the Data RAM address only, an offset can added to the requested address (Address Base).

Instruction "store source dest ofs":

Copy the value from a register in the internal memory map to the Data RAM. For the Data RAM address only, an offset can added to the requested address (Address Base).

## **Software - Instruction Set Overview**

- √ 93 instructions in 7 categories:

- 1. Arithmetic Logic Unit (27)

- 2. Configuration (29)

- 3. Diagnostic (3)

- 4. Interrupt and Subroutine (6)

- 5. Jump (16)

- 6. Load (9)

- 7. Wait (3)

## 3 Wait Instructions

- cwef create wait table entry far

- cwer create wait table entry relative

- 3. wait wait until a condition is verified

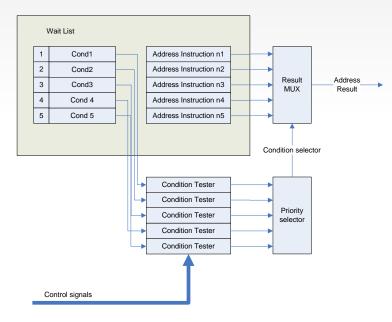

# ...ow Control Instructions: Wait

- Each "µCore has a 5 row "wait table".

- Each row can be loaded with a condition and a destination ("cwer/f").

- When a "wait" instruction is executed, the flow is stopped until one of the enabled condition is true. The flow resumes at the address in the same row of the fulfilled condition.

#### Instruction "cwer/f dest cond row":

Load the selected line in the wait table with the destination address and condition specified as parameters.

#### Instruction "wait mask":

• Stop the code execution and enables the row of the wait table specified by mask parameter. When the condition on one of the enabled rows is met, the code execution resumes at the corresponding address.